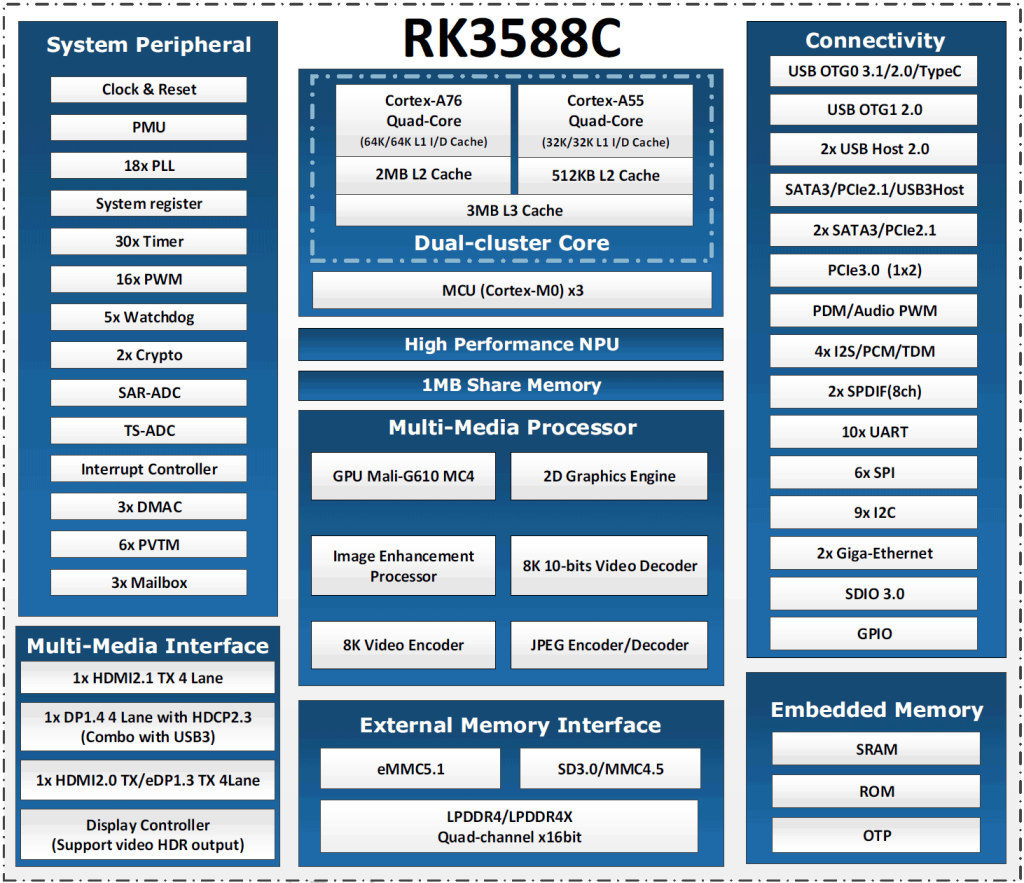

RK3588C 是一款用于 NVR 和边缘计算设备的低功耗、高性能处理器,集成了四核 Cortex-A76 和四核 Cortex-A55 以及单独的 NEON 协处理器。许多嵌入式强大的硬件引擎为高端应用提供优化的性能。RK3588C 支持 8K@60fps 的 H.265 和 VP9 解码器、8K@30fps 的 H.264 解码器和 4K@60fps 的 AV1 解码器,还支持 8K@30fps 的 H.264 和 H.265 编码器、高质量的 JPEG 编码器/解码器、专用图像预处理器和后处理器。

嵌入式 3D GPU 使RK3588C与 OpenGLES 1.1、2.0 和 3.2、OpenCL 2.2 和 Vulkan1.2 完全兼容。带有 MMU 的特殊 2D 硬件引擎将最大限度地提高显示性能并提供非常流畅的操作。内置 NPU 支持 INT4/INT8/INT16/FP16 混合运行,计算能力高达 6TOPs。此外,凭借其强大的兼容性,可以轻松转换基于 TensorFlow/MXNet/PyTorch/Caffe 等一系列框架的网络模型。

嵌入式 3D GPU 使RK3588C与 OpenGLES 1.1、2.0 和 3.2、OpenCL 2.2 和 Vulkan1.2 完全兼容。带有 MMU 的特殊 2D 硬件引擎将最大限度地提高显示性能并提供非常流畅的操作。内置 NPU 支持 INT4/INT8/INT16/FP16 混合运行,计算能力高达 6TOPs。此外,凭借其强大的兼容性,可以轻松转换基于 TensorFlow/MXNet/PyTorch/Caffe 等一系列框架的网络模型。

RK3588C具有高性能四通道外部存储器接口 (LPDDR4/LPDDR4X),能够维持苛刻的存储器带宽,还提供一整套外设接口来支持非常灵活的应用。

微处理器

- 四核 ARM Cortex-A76 MPCore 处理器和四核 ARM Cortex-A55 MPCore 处理器,均为高性能、低功耗和缓存应用处理器

- DSU(DynamIQ 共享单元)包括 L3 内存系统、控制逻辑和外部接口,以支持 DynamIQ 集群

- 完全实现 ARM 架构 v8-A 指令集、ARM Neon Advanced SIMD(单指令、多数据)支持,以加速媒体和信号处理

- ARMv8 加密扩展

- Trustzone 技术支持

- 每个 Cortex-A76 集成 64KB L1 指令缓存、64KB L1 数据缓存和 512KB L2 缓存

- 每个 Cortex-A55 集成 32KB L1 指令缓存、32KB L1 数据缓存和 128KB L2 缓存

- 四核 Cortex-A76 和四核 Cortex-A55 共享 3MB L3 缓存

- CPU 核心系统有 8 个独立的电源域,支持内部电源开关,并根据不同的应用场景从外部开启/关闭

- PD_CPU_0:第 1 个 Cortex-A55 + Neon + FPU + L1/L2 I/D 缓存

- PD_CPU_1:第 2 个 Cortex-A55 + Neon + FPU + L1/L2 I/D 缓存

- PD_CPU_2:第 3 个 Cortex-A55 + Neon + FPU + L1/L2 I/D 缓存

- PD_CPU_3:第 4 个 Cortex-A55 + Neon + FPU + L1/L2 I/D 缓存

- PD_CPU_4:第 1 个 Cortex-A76 + Neon + FPU + L1/L2 I/D 缓存

- PD_CPU_5:第 2 个 Cortex-A76 + Neon + FPU + L1/L2 I/D 缓存

- PD_CPU_6:第 3 个 Cortex-A76 + Neon + FPU + L1/L2 I/D 缓存

- PD_CPU_7:第 4 个 Cortex-A76 + Neon + FPU + L1/L2 I/D 缓存

- 三个支持 DVFS 的隔离电压域,一个用于 A76_0 和 A76_1,一个用于 A76_2 和 A76_3,另一个用于 DSU 和 Cortex-A55。

1.2.2 内存组织

- 内部片上存储器

- BootRom 系列

- 支持从以下设备启动系统:

- SPI 接口

- eMMC 接口

- SD/MMC 接口

- 支持从以下设备启动系统:

- BootRom 系列

-

-

- 支持通过以下界面下载系统代码:

- USB OTG 接口

- 在 VD_LOGIC 的电压域中共享内存

- VD_PMU 的 PMU SRAM,适用于低功耗应用

- 支持通过以下界面下载系统代码:

-

- 外部片外存储器

-

- 动态内存接口

- 兼容 JEDEC 标准 LPDDR4/LPDDR4X

- 支持四个通道,每个通道 16 位数据宽度

- 每个通道最多支持 2 个列(片选)

- 总共高达 32GB 的地址空间

- 低功耗模式,例如 SDRAM 的掉电和自刷新

- eMMC 接口

- 完全符合 JEDEC eMMC 1 和 eMMC 5.0 规范

- 向后兼容 eMMC 51 及更早版本规范。

- 支持 HS400、HS200、DDR50 和传统操作模式

- 支持三种数据总线宽度:1bit、4bits 或 8bits

- SD/MMC 接口

- 兼容 0, MMC ver4.51

- 数据总线宽度为 4 位

- 灵活的串行闪存接口 (FSPI)

- 支持从串行闪存设备传输数据

- 支持 1bit、2bits 或 4bits 数据总线宽度

- 支持 2 个芯片选择

- 动态内存接口

系统组件

- MCU

- 内置三个 Cortex-M0 MCU RK3588C

- VD_PMU MCU 集成了 16KB 缓存和 16KB TCM

- VD_NPU MCU 集成 16KB 缓存和 64KB TCM

- PD_CENTER集成 32KB TCM 的 MCU

- 集成可编程中断控制器,所有连接到 CPU GIC 的 IRQ 线也连接到 VD_PMU(PMU_M0) 和 PD_CENTER(DDR_M0) 中的 MCU

- 带 JTAG 接口的集成调试控制器

- CRU(时钟和复位单元)

- 支持总共 18 个 PLLs 来生成所有 clocks

- 一个具有 24MHz 时钟输入的振荡器

- 支持单个组件的时钟门控控制

- 支持整个芯片的全局软复位控制,也支持每个元件的单独软复位

- PMU(电源管理单元)

- 多种可配置的工作模式,通过不同频率或自动时钟门控控制或电源域开/关控制来节省功率

- 不同模式下的大量唤醒源

- 支持 10 个独立的电压域

- 支持 45 个独立的电源域,可根据不同的应用场景通过软件进行上电/下电

- Timer

- 支持 12 个安全定时器,具有 64 位计数器和基于中断的操作

- 支持 18 个非安全定时器,具有 64 位计数器和基于中断的操作

- 支持两种操作模式:每个定时器的自由运行和用户自定义计数

- 支持定时器工作状态可检查

- PWM的

- 支持 16 个片上 PWM(PWM0~PWM15),具有基于中断的操作

- 可编程的预缩放操作到总线时钟,然后进一步缩放

- 嵌入式 32 位定时器/计数器功能

- 支持捕获模式

- 支持连续模式或单次模式

-

- 提供参考模式并输出各种占空比波形

- 针对 PWM3、PWM7、PWM11、PWM15 的 IR 应用进行了优化

- 看门狗

- 32 位看门狗计数器

- 计数器从预设值倒计时到 0 以指示超时的发生

- 发生超时时,WDT 可以执行两种类型的操作:

- 生成系统重置

- 首先生成一个中断,如果在发生第二次超时时服务程序没有清除此中断,则生成系统重置

- 共有 5 个 CPU 和 MCU 看门狗

- 中断控制器

- 支持来自内部不同组件的 12 个 PPI 中断源和 480 个 SPI 中断源RK3588C

- 支持 16 个软件触发中断

- 输入中断电平是固定的,对 SPI 为高电平敏感,对 PPI 为低电平敏感

- 支持每个中断源的不同中断优先级,并且它们始终可通过软件编程

- DMAC

- 基于微代码编程的 DMA

- 支持链表 DMA 功能,完成 scatter-gather 传输

- 支持数据传输类型,包括内存到内存、内存到外设、外设到内存

- 外设系统共有三个嵌入式 DMA 控制器

- 每个 DMAC 都具有以下特点:

- 支持 8 个通道

- 32 来自外围设备的硬件请求

- 2 个中断输出

- 支持 TrustZone 技术和每个 DMA 通道的可编程安全状态

- 安全系统

- 嵌入式双密码引擎

- 支持链接列表项 (LLI) DMA 传输

- 支持 SHA-1、SHA-256/224、SHA-512/384、MD5、SM3 和硬件填充

- 支持 SHA-1、SHA-256、SHA-512、MD5、SM3 的 HMAC,带硬件填充

- 支持AES-128, AES-192, AES-256加密和解密密码

- 支持 AES ECB/CBC/OFB/CFB/CTR/CTS/XTS/CCM/GCM/CBC-MAC/CMAC模式

- 支持 SM4 ECB/CBC/OFB/CFB/CTR/CTS/XTS/CCM/GCM/CBC-MAC/CMAC模式

- 支持DES和TDES密码,具有ECB/CBC/OFB/CFB模式

- 支持高达 4096 位的 RSA/ECC/SM2 PKA 数学运算

- 支持生成随机数

- 嵌入式双密码引擎

-

- 支持钥匙梯,保证钥匙安全

- 支持所有 DDR 类型的数据加扰

- 支持安全的 OTP

- 支持安全调试

- 支持安全的 DFT 测试

- 支持安全操作系统

- 除了 CPU,SoC 中的其他主站也可以通过软件可编程来支持安全和非安全模式

- SoC 中的一些从属组件只能由安全主站寻址,而其他从属组件可以通过软件可编程由安全主站或非安全主站寻址

- 系统 SRAM(共享内存),部分空间仅在安全模式下寻址

- 外部 DDR 空间可分为 16 个部分,每个部分都可以由每个主站进行软件编程

- Mailbox

- SoC 中的三个邮箱,用于服务 CPU 和 MCU 通信

- 每个邮箱支持 4 个 mailbox 元素,每个元素包括 1 个数据字、1 个命令字 register 和 1 个可表示一个中断的标志位

- 提供 32 个锁寄存器,供软件用于指示邮箱是否被占用

- 解压缩

- 支持解压缩 GZIP 文件

- 支持解压缩 LZ4 文件,包括 LZ4 Frame 格式的 General Structure 和 Legacy Frame 格式。

- 支持以 DEFLATE 格式解压缩数据

- 支持以 ZLIB 格式解压缩数据

- 支持 LZ4 解压过程中的 Hash32 检查

- 支持解压后数据的限制大小功能,防止解压过程中内存被恶意破坏

视频编解码器

- 视频解码器

- MPEG-1、MPEG-2、MPEG-4、263、H.264、H.265、VC-1、VP9、VP8、MVC、AV1 的实时视频解码器

- MMU 嵌入式

- 多通道并行解码器,分辨率较低

- 264 个 AVC/MVC 主 10 个 L6.0:8K@30fps (7680×4320)(2)

- VP9 配置文件0/21 : 8K@60fps (7680×4320)

- 265 HEVC/MVC Main10 L6.1:8K@60fps (7680×4320)

- AVS2 配置文件0/2 2.6:8K@60fps (7680×4320)

- AV1 主要配置文件 8/10bit3 : 4K@60fps (3840×2160)

- MPEG-2 最高 MP : 1080p@60fps (1920×1088)

- MPEG-1 最高 MP : 1080p@60fps (1920×1088)

- VC-1 最高 AP 级别 3 : 1080p@60fps (1920×1088)

- VP8 版本2 : 1080p@60fps (1920×1088)

- 视频编码器

- 实时 265/H.264 视频编码

- 最多支持 8K@30fps

- 多通道并联编码器,分辨率较低

JPEG 编解码器

- JPEG 编码器

- 基线 (DCT 顺序)

- 编码器尺寸从 96×96 到 8192×8192(67M 像素)

- 每秒高达 9000 万像素

- 嵌入式 4 个编码器单元

- JPEG 解码器

- 解码器大小从 48×48 到 65536×65536

- 支持 YUV400/YUV411/YUV420/YUV422/YUV440/YUV444

- 支持高达 1080P@280fps 和每秒 5.6 亿像素

- 支持 MJPEG

- 嵌入式 4 个编码器单元

神经过程单元

- 处理性能高达 6 TOPS 的神经网络加速引擎

- 包含三核 NPU 核,并支持三核协同工作、双核协同工作、独立工作

- 支持整数 4、整数 8、整数 16、浮点数 16、Bfloat 16 和 tf32 运算

- 嵌入式 384KBx3 内部缓冲区

- 多任务、多场景并行

- 支持深度学习框架:TensorFlow、Caffe、Tflite、Pytorch、Onnx NN、Android NN 等。

- 一个隔离电压域,支持 DVFS

图形引擎

- 3D 图形引擎

- ARM Mali-G610 MP4

- 高性能 OpenGLES 1、2.0 和 3.2、OpenCL 2.2、Vulkan1.2 等。

- 嵌入式 4 个着色器核心,带有共享的分层 tiler

- 提供 4 个 256KB 大小的 MMU 和 L2 缓存

- 最新的 Valhall 建筑

- ARM 帧缓冲压缩 (AFBC) 3

- 支持嵌入式 MCU 的串行线调试

- 一个隔离电压域,支持 DVFS

- 2D 图形引擎

- 源格式:ARGB/RGB888/RGB565/YUV420/YUV422/BPP

- 目标格式:ARGB/RGB888/RGB565/YUV420/YUV422

- 最大分辨率:8192×8192 源,4096×4096 目标

- 块传输和透明模式

- 使用渐变填充和图案填充进行颜色填充

- Alpha 混合模式,包括全局 Alpha、每像素 Alpha(单独颜色/Alpha 通道)和淡化

- 任意非整数缩放比例,从 1/8 到 8

- 0, 90, 180, 270度旋转,X镜,Y镜和旋转操作

- ROP2、ROP3、ROP4

- 支持 4k/64k 页面大小 MMU

- 图像增强处理器

- 图像格式

- 输入数据:YUV420/YUV422、半平面/平面、UV 交换

- 输出数据:YUV420/YUV422、半平面、UV 交换、平铺模式

- YUV 下采样从 422 到 420 的转换

- 动态图像的最大分辨率高达 1920×1080

- 去隔行扫描

- 图像格式

视频输入接口

- DVP 接口

- 1 个 8/10/12/16 位标准 DVP 接口,最高 150MHz 输入数据

- 支持 601/BT.656 和 BT.1120 VI 接口

- 支持极性pixel_clk、hsync、vsync 可配置

显示界面

- 1 个 HDMI TX 接口

- 支持一个 1 个HDMITX 接口

- 支持 1 FRL 模式的 x3 和 x4 配置

- 向后兼容 1 个 TMDS 及更早版本规范

- 支持 HDMI FRL 的所有数据速率:3、6、8、10 和 12Gbps

- HDMI TX 最高支持 7680×4320@60Hz 个

- 支持 HDMI TX 的 RGB/YUV(最高 10bit)格式

- 支持 DSC 2a 用于 HDMI TX

- 支持 3 个 HDMI TX

- eDP1.4 TX 接口

- 支持 1 个 eDP1.4 TX 组合接口,但每个接口的 HDMI 和 eDP 不能同时工作

- 支持 eDP 的 x1、x2 和 x4 配置

- 支持 62Gbps、2.7Gbps 和 5.4Gbps 的 eDP

- 最高支持 4096×2160@60Hz 个 HDMI TX 和 4K@60Hz 个 eDP

- 支持 HDMI TX 的 RGB/YUV(最高 10bit)格式

- 支持 RGB、YCbCr 4:4:4、YCbCr 4:2:2 和每分量 8/10 位视频格式,用于 eDP

- 支持 DSC 2a 用于 HDMI TX

- 支持 3 个 HDMI TX 和 HDCP1.3 用于 eDP

- HDMI TX 接口视频定时要求

- 建议遵循 CTA-861 标准

- 当视频时序不标准时,建议使用 HSYNC/HBP/HFP 4 像素一致

- DP TX 接口

- 支持 1 个 DP TX 4a 接口,与 USB3.1 Gen1 组合

- 每个接口支持 1/2/4 通道

- 支持 62Gbps、2.7Gbps、5.4Gbps 和 8.1Gbps 串行器

- 支持高达 7680×4320@30Hz

- 支持 RGB/YUV(最高 10bit)格式

- 支持单流传输 (SST)

- 在 USB Type-C 上支持 DP Alt 模式

- 支持 3、HDCP 1.3

- 接口视频定时要求

- 建议遵循 CTA-861 标准

- 当视频时序不标准时,HSYNC/HBP/HFP 的最小值为 16 像素

- 1120 视频输出接口

- 支持高达 1920×1080@60Hz

- 高达 150MHz 的数据速率

视频输出处理器

- 视频端口

- 视频端口 0,最大输出分辨率:7680×4320@60Hz

- 视频端口 1,最大输出分辨率:4096×4320@60Hz

- 视频端口 2,最大输出分辨率:4096×4320@60Hz

- 视频端口 3,最大输出分辨率:2048×1080@60Hz

- 集群 0/1/2/3

- 最大输入和输出分辨率 4096×4320

- 支持 AFBCD

- 支持 RGB/YUV/YUYV 格式

- 支持放大/缩小比例 4~1/4

- 支撑旋转

- 智能 0/1/2/3

- 最大输入和输出分辨率 4096×4320

- 支持 RGB/YUV/YUYV 格式

- 支持放大/缩小比例 8~1/8

- 支持 4 个区域

- 覆盖

- 最多支持 8 层叠加:4 个集群/4 个 esmart

- 支持 RGB/YUV 域叠加

- 后处理

- HDR (高动态范围)

- HDR10/HDR HLG

- HDR2SDR/SDR2HDR

- 3D-LUT/P2I/CSC/BCSH/抖动/CABC/Gamma/彩条

- HDR (高动态范围)

- 回信

- 格式:ARGB8888/RGB888/RGB565/YUV420

- 最大分辨率:1920×1080

- VOP 接口视频定时要求

- HACTIVE 必须以 4 像素对齐

- 当启用拆分模式或 MIPI 双通道模式或 yuv420 格式时,POST HSYNC/HBP/HFP 必须对齐 2 像素

- 启用 MIPI DSC 视频模式时,POST HSYNC/HBP/HFP 的最小值为 16 像素,DSC_SYS_CTRL HSYNC/HBP/HFP 的最小值为 8 像素

音频接口

- I2S1 带 8 个通道

- 多达 8 个通道 TX 和 8 个通道 RX 路径

- 音频分辨率从 16 位到 32 位

- 采样率高达 192KHz

- 提供主从工作模式,软件可配置

- 支持 3 种 I2S 格式(正常、左对齐、右对齐)

- 支持 4 种 PCM 格式(early、late1、late2、late3)

- 支持 TDM 正常、1/2 周期左移、1 周期左移、2 周期左移、右移模式串行音频数据传输

- I2S、PCM 和 TDM 模式不能同时使用

- I2S0 带 4 个通道

- 多达 4 个通道 TX 或 4 个通道 RX 路径

- 音频分辨率从 16 位到 32 位

- 采样率高达 192KHz

- 提供主从工作模式,软件可配置

- 支持 3 种 I2S 格式(正常、左对齐、右对齐)

- 支持 4 种 PCM 格式(early、late1、late2、late3)

- 支持 TDM 正常、1/2 周期左移、1 周期左移、2 周期左移、右移模式串行音频数据传输

- I2S、PCM 和 TDM 模式不能同时使用

- I2S2/I2S3 带 2 个通道

- 最多 2 个 TX 通道和 2 个 RX 通道

- 音频分辨率从 16 位到 32 位

- 采样率高达 192KHz

- 提供主从工作模式,软件可配置

- 支持 3 种 I2S 格式(正常、左对齐、右对齐)

- 支持 4 种 PCM 格式(early、late1、late2、late3)

- I2S 和 PCM 不能同时使用

- SPDIF0/SPDIF1

- 支持将两个 16 位音频数据存储在一个 32 位宽的位置

- 支持双相格式立体声音频数据输出

- 支持 16 至 31 位音频数据左对齐或右对齐,在 32 位宽的采样数据缓冲区中对齐

- 在线性 PCM 模式下支持 16、20、24 位音频数据传输

- 支持非线性 PCM 传输

- PDM0/PDM1

- 多达 8 个通道

- 音频分辨率从 16 位到 24 位

- 采样率高达 192KHz

- 支持 PDM 主站接收模式

- 数字音频编解码器

- 支持 2 通道数字 DAC

- 支持 I2S/PCM 接口、主从模式

- 支持 16 位采样分辨率

- 支持每个数字 DAC 通道的三种混合模式

- 支持音量控制

- VAD(语音活动检测)

- 支持从 I2S/PDM 读取语音数据

- 支持语音振幅检测

- 支持多麦克风阵列数据存储

- 支持 A 级组合中断

连接方式

- SDIO 接口

- 兼容SDIO3.0协议

- 4 位数据总线宽度

- GMAC 10/100/1000M 以太网控制器

- 支持两个以太网控制器

- 通过 RGMII 接口支持 10/100/1000 Mbps 数据传输速率

- 通过 RMII 接口支持 10/100 Mbps 数据传输速率

- 支持全双工和半双工操作

- USB3.1 第 1 代

- 支持 1 个 Gen1,相当于 USB3.2 Gen1 和 USB3.0,数据速率高达 5Gbps

- 嵌入式 1 1 OTG 接口,与 DP TX (USB3OTG_0) 组合

- 嵌入式 1 1 主机接口,与 Combo PIPE PHY2 组合

(USB3OTG_2)

- 兼容规格

- 通用串行总线 0 规范,修订版 1.0

- 通用串行总线规范,修订版 0(不包括 USB3OTG_2)

- 通用串行总线 (xHCI) 的可扩展主机控制器接口,修订版 1

- 支持 Control/Bulk(包括流)/Interrupt/Isochronous Transfer

- USB3.1 Gen1 的同步 IN 和 OUT 传输

- 描述符缓存和数据预取用于提高高延迟系统中的系统性能

- USB 0(不包括 USB3OTG_2 USB3.1 Gen1)和 U0、U1、U2 和 U3 状态的 LPM 协议

- USB3.1 Gen1 设备特性

- 最多 10 个 IN 终端节点,包括控制终端节点 0

- 最多 6 个 OUT 端点,包括控制端点 0

- 最多 16 个终端节点传输资源,每个终端节点对应 1 个

- 灵活的端点配置,适用于多种应用程序/USB 设置配置模式

- 硬件处理 ERDY 和突发

- 基于流的批量终端节点,控制器自动启动数据移动

- 数据缓冲区中具有等时数据的等时端点

- 灵活的描述符,具有丰富的功能集,支持缓冲区中断调节、多次传输、同步、控制和分散缓冲支持

- USB3.1 Gen1 xHCI 主机功能

- 最多支持 64 台设备

- 支持 1 个中断器

- 支持 1 个 0 端口(不包括 USB3OTG_2)和 1 个 Super-Speed 端口

- 支持标准或开源 xHCI 和类驱动程序

- USB3.1 Gen1 双重角色设备 (DRD) 功能

- 静态设备操作

- 静态主机操作

- 1/USB2.0 OTG A 设备和基于 ID 的 B 设备,USB3OTG_2仅支持 USB3.1 Gen1

- 不支持 1/USB2.0 OTG 会话请求协议 (SRP)、主机协商协议 (HNP) 和角色交换协议 (RSP)

- 其他功能

- USB2.0PHY 支持电池充电检测

- USB3OTG_0支持 USB Type-C 和 DP Alt 模式

- USB3OTG_2 PHY 组合与 PCIE 和 SATA

- USB20 OTG

- 兼容规格

- 通用串行总线规范,修订版 0(不包括 USB3OTG_2)

- 通用串行总线 (xHCI) 的可扩展主机控制器接口,修订版 1

- 支持 Control/Bulk(包括流)/Interrupt/Isochronous Transfer

- 描述符缓存和数据预取用于提高高延迟系统中的系统性能

- 其他功能

- 0 PHY 支持电池充电检测

- 双重角色设备 (DRD) 功能

- 静态设备操作

- 静态主机操作

- 0 OTG A 设备和 B 设备(基于 ID)

- 不支持 0 OTG 会话请求协议 (SRP)、主机协商协议 (HNP) 和角色交换协议 (RSP)

- 兼容规格

- USB 2.0设备功能

- 最多 10 个 IN 终端节点,包括控制终端节点 0

- 最多 6 个 OUT 端点,包括控制端点 0

- 最多 16 个终端节点传输资源,每个终端节点对应 1 个

- 灵活的端点配置,适用于多种应用程序/USB 设置配置模式

- USB 2.0 xHCI 主机功能

- 最多支持 64 台设备

- 支持 1 个中断器 支持 1 个 USB2.0 端口

- USB 2.0主机

- 兼容 USB 2.0规范

- 支持两个 USB 2.0主机

- 支持高速 (480Mbps)、全速 (12Mbps) 和低速 (1.5Mbps) 模式

- 支持增强型主机控制器接口规范 (EHCI) 修订版1.0

- 支持开放主机控制器接口规范 (OHCI) 修订版1.0a

-

- 组合 PIPE PHY 接口

- 支持三个带有 PCIe2.1/SATA3.0/USB3.1 控制器的 Combo PIPE PHY

- PCIe2.1接口

- 与 PCI Express 基本规范修订版2.1兼容

- 每个 1 个接口支持 1 个通道

- 仅支持根复合体 (RC)

- 支持 5Gbps 数据速率

- SATA 接口

- 与串行 ATA 1 和 AHCI 修订版 1.3.1 兼容

- 支持 eSATA

- 每个 SATA 接口支持 1 个端口

- 支持 6Gbps 数据速率

- PCI E3.0接口

- 与 PCI Express 基本规范修订版3.0兼容

- 支持双操作模式:Root Complex (RC) 和 End Point (EP)

- 支持数据速率:5Gbps(PCIe1.1)、5Gbps(PCIe2.1)、8Gps(PCIe3.0)

- 支持 1x 2lanes、2x 1lanes 的聚合和分叉

- SPI 接口

- 支持 5 个 SPI 控制器(SPI0-SPI4)

- 支持两个片选输出

- 支持串主和串从模式,软件可配置

- I2C 主控制器

- 支持 9 个 I2C 主控(I2C0-I2C8)

- 支持 7 位和 10 位地址模式

- 软件可编程时钟频率

- I2C 总线上的数据在标准模式下可以以高达 100k bits/s 的速率传输,在快速模式下可以高达 400k bits/s 的速率传输

- UART 接口

- 支持 10 个 UART 接口(UART0-UART9)

- 嵌入两个 64 字节 FIFO,分别用于 TX 和 RX 操作

-

- 支持 5bit、6bit、7bit、8bit 串行数据传输或接收

- 标准异步通信位,如 start、stop 和 parity

- 支持不同的 UART 操作输入时钟,以获得高达 4Mbps 的波特率

- 支持所有 UART 的自动流控模式

其他

- 多组 GPIO

- 所有 GPIO 都可用于生成中断

- 支持电平触发和边沿触发中断

- 支持电平触发中断的可配置极性

- 支持可配置的上升沿、下降沿和两个边沿触发中断

- 支持可配置的拉动方向(一个弱上拉和一个弱下拉)

- 支持可配置的驱动强度

- 温度传感器 (TS-ADC)

- 支持用户自定义模式和自动模式

- 在用户定义模式下,start_of_conversion可以完全由软件控制,也可以由硬件生成。

- 在自动模式下,可以配置报警(高/低温)中断的温度

- 在自动模式下,系统复位的温度可以配置

- 支持 7 通道 TS-ADC,每个通道的温度标准可配置

- -40~125°C 温度范围和 1°C 温度分辨率

- 逐次逼近型 ADC (SARADC)

- 12 位分辨率

- 高达 1MS/s 的采样率

- 4 个单端输入通道

- 一次性密码

- 支持 32Kbit 空间和更高的 4k 地址空间是不安全的

- 支持在安全模型中读取和编程字掩码

- 支持最大 32 位 OTP 程序操作

- 支持最大 16 字的 OTP 读取操作

- 可以读取 Program 和 Read 状态

- 程序失败地址记录

- 封装类型

- FCCSP766L (本体:17mm x 19mm;球尺寸:3mm;球间距:0.6mm&0.65mm)