瑞芯微RK1808芯片简介 Introduction To Rockchip RK1808

1.1 Overview

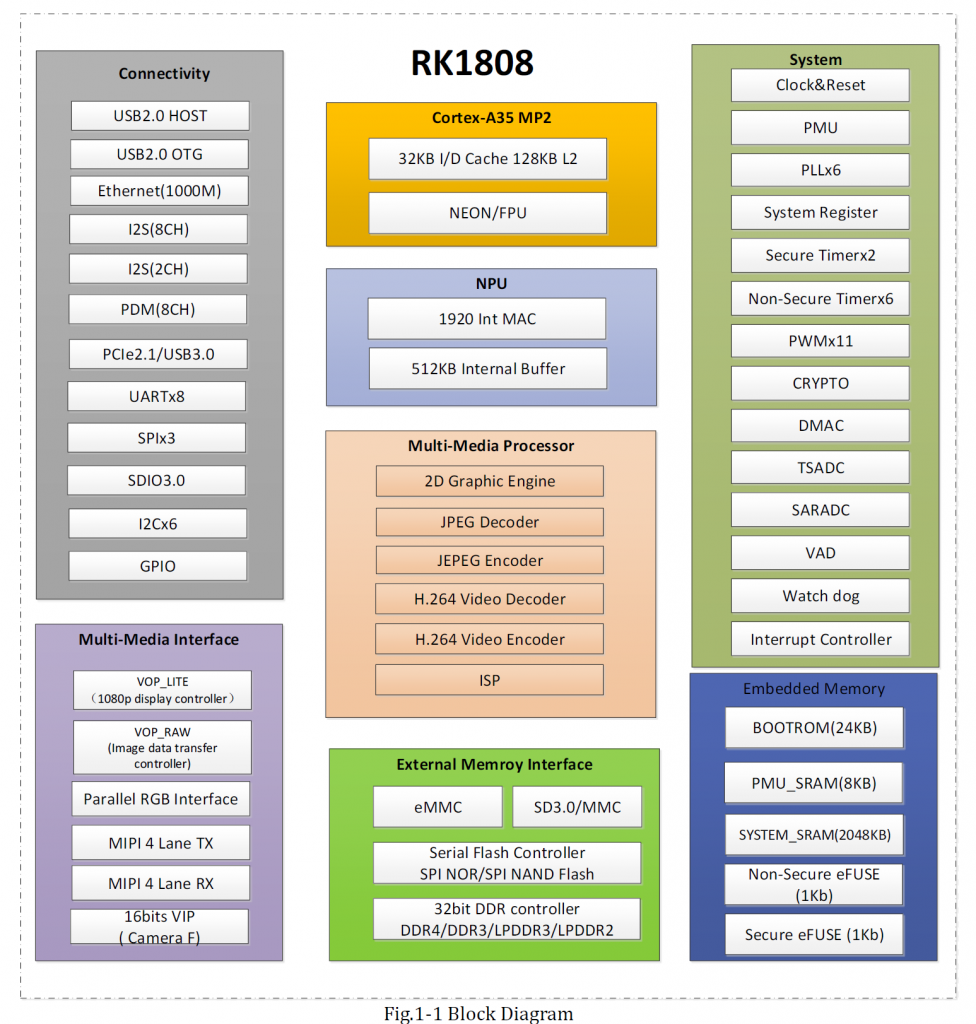

RK1808 is a high-performance, low power processor for neural network inference. Especially, it is one of current leading solution for mobile device by providing complementary neural network hardware accelerator.

Equipped with one powerful neural network process unit(NPU), it makes RK1808 easy programming and compatible with mainstream platforms in the market, such as caffe, tensor flow, and so on.

1.2 Features

The features listed below which may or may not be present in actual product, may be subject to the third party licensing requirements. Please contact Rockchip for actual product feature configurations and licensing requirements.

1.2.1 Microprocessor

1.2.1 Microprocessor

- Dual-core ARM Cortex-A35 CPU

- ARM Neon Advanced SIMD (single instruction, multiple data) support for accelerated media and signal processing computation

- Include VFP v4 hardware to support single and double-precision operations

- 128KB unified system L2 cache

- Integrated 32KB L1 instruction cache, 32KB L1 data cache with 4-way set associative

- One isolated voltage domain include

- Separate power domains for CPU core system to support internal power switch

- PD_CPU0: 1st Cortex-A35 + Neon + FPU + L1 I/D Cache

- PD_CPU1: 2nd Cortex-A35 + Neon + FPU + L1 I/D Cache

- One isolated voltage domain includes Dual Core CPU, L2 cache and other logics to support DVFS and can externally turn on/off based on different application

1.2.2 Neural Process Unit

- Support max1920 Int8 MAC operations per cycle

- Support max 64 FP16 MAC operations per cycle

- Support max192 Int16 MAC operations per cycle

- 512KB internal buffer

- One isolated voltage domain to support DVFS

1.2.3 On Chip Memory

- Internal BootRom

- Used for storing boot code and support system boot from the following interface:

- SFC interface

- Used for storing boot code and support system boot from the following interface:

The Serial Flash Controller (SFC) is used to control the data transfer between the SoC system and the serial NOR/NAND flash device.

- eMMC interface

- SDMMC interface

- SYSTEM_SRAM

- Size: 2MB

- PMU_SRAM

- Size: 8KB

1.2.4 External Memory or Storage device

- Dynamic Memory Interface (DDR3/DDR3L/LPDDR2/LPDDR3/DDR4)①

- Compatible with JEDEC standards

- Compatible with DDR3-1600/DDR3L-1600/ LPDDR2-1066 /LPDDR3-1600/DDR4- 2133

- Support 32-bit data width, 2 ranks (chip selects), max 4GB addressing space per rank, total addressing space is 4GB(max)

- eMMC interface

- Compatible with eMMC specification 4.41, 51

- Support data bus width: 1-bit, 4-bit or 8-bit

- Support up to max 150MB/s data transfer rates

- SD/MMC interface

- Compatible with SD3.0, MMC 51

- Data bus width is 4bits

- Serial FLASH interface

- Support x1,x2,x4 data bits mode

- Support 1 chip select

1.2.5 System Component

- CRU (clock & reset unit)

- One oscillator with 24MHz clock input

- Provide clock gating control for individual components

- Support global soft-reset control for whole chip, also individual soft-reset for each component.

- PMU(Power Management Unit)

- Manage on operating on 4 separate voltage domains for the digital logic circuit: VD_CORE/VD_LOGIC/VD_NPU/VD_PMU

- Provide powering up/down function for 7 power domains, which are included in the 4 voltage domains independently, to save

- PD_CPU0 and PD_CPU1 in VD_CORE

- PD_VIO, PD_PCIe, PD_VPU and PD_DDR in VD_LOGIC

- Timer

- Support 6 64-bit timers for non-secure application

- Support 2 64-bit timers for secure application

- Support two operation modes: free-running and user-defined count

- PWM

- Support 11 on-chip PWMs(PWM0~PWM3,PWM5~PWM11)

- Embedded 32-bit timer/counter facility

- Support capture mode

- Support continuous mode or one-shot mode

- Optimized for IR receiving application for PWM3, PWM7 and PWM11

- Watchdog

- One Watchdog for non-secure application

- One Watchdog for secure application

- 32-bit watchdog counter

- Counter counts down from a preset value to 0 to indicate the occurrence of a timeout

- WDT can perform two types of operations when timeout occurs:

- Generate a system reset

- First generate an interrupt and if this is not cleared by the service routine by the time a second timeout occurs then generate a system reset

- Totally 16 defined-ranges of main timeout period

- Interrupt Controller

- Support 256 SPI (Shared Peripheral Interrupts) interrupt sources input from different components

- Support 16 software-triggered interrupts

- Two interrupt outputs (nFIQ and nIRQ) separately for each Cortex-A35, both are low-level sensitive

- DMAC

- One embedded DMA controller for system

- Linked list DMA function is supported to complete scatter-gather transfer

- Support data transfer types with memory-to-memory, memory-to-peripheral, peripheral-to-memory

- DMAC features:

- Support 8 channels

- 31 hardware request from peripherals

- 2 interrupt output

- Trusted Execution Environment system

- Support TrustZone technology for the following components

- Cortex-A35, support secure and non-secure mode, switch by software

- System general DMAC, support dedicated channels work only in secure mode

- Secure eFUSE, only can be accessed by Cortex-A35 in secure mode

- SYSTEM_SRAM, part of space is addressed only in secure mode, specific size is software-programmable

- Firewall is embedded to manage other master/slave module

- Support TrustZone technology for the following components

- Cipher engine

- Support SHA-1, SHA-256/224, MD5 with hardware padding

- Support Link List Item (LLI) DMA transfer

- Support SHA-1, SHA-256/224,MD5 with hardware padding

- Support HMAC of SHA-1, SHA-256, MD5 with hardware padding

- Support AES-128 encrypt & decrypt cipher

- Support AES ECB/CBC/OFB/CFB/CTR/CTS/XTS mode

- Support up to 4096 bits PKA mathematical operations for RSA/ECC

- Support up to 8-channels configuration

- Support Up to 256 bits TRNG output

- Support data scrambling for DDR3/DDR3L/LPDDR3/LPDDR2/DDR4

- Support secure boot

- Support secure debug

1.2.6 Video CODEC

- Video Decoder

- Support H.264/AVC Base/Main/High@level4.2

- Up to 1920×1080@60fps

- Video Encoder

- Support H.264 video encoder at BP/MP/HP@level4.1

- Up to 1920×1080@30fps

1.2.7 JPEG CODEC

- JPEG decoder

- Decoder size is from 48×48 to 8176×8176(66.8Mpixels)

- Support JPEG ROI (region of image) decode

- JPEG encoder

- Baseline (DCT sequential)

1.2.8 Graphic Engine

- 2D Graphics Engine:

- Data format

- Support input of ARGB/RGB888/RGB565/RGB4444/RGB5551/YUV420/YUV422

- Support input of YUV422SP(10-bit)/YUV420SP(10-bit)

- Support output of ARGB/RGB888/RGB565/RGB4444/RGB5551/YUV420/YUV422

- Pixel Format conversion, 601/BT.709

- Data format

- Dither operation

- Max resolution: 8192×8192 source, 4096×4096 destination

- Scaling

- Support scaling up and down

- Arbitrary non-integer scaling ratio,from 1/8 to 8

- Rotation

- 0, 90, 180, 270 degree rotation

- x-mirror, y-mirror& rotation operation

- BitBLT

- Block transfer

- Color palette/Color fill, support with alpha

- Transparency mode (color keying/stencil test, specified value/value range)

- Two source BitBLT:

- A+B=B only BitBLT, A support rotate&scale when B fixed

- A+B=C second source (B) has same attribute with (C) plus rotation function

- Alpha Blending

- New comprehensive per-pixel alpha(color/alpha channel separately)

- SRC1(R2Y)&&SRC0(YUV) alpha into DST(YUV)

- Fading

1.2.9 Video input interface

- Interface and video input processor

- Support up to 16-bit DPI interface (digital parallel input)

- Support MIPI CSI RX interface

- Support VIP block(Camera Interface)

- Support ISP block(Image Signal Processor)

- Support DPI interface to VIP block

- Support DPI interface to ISP block

- Support MIPI CSI RX interface to ISP block

- Support the following two mode simultaneously

- DPI interface with VIP

- MIPI CSI RX interface with ISP

- DPI Interface

- Support 8-bit/10-bit/12-bit/16-bit input

- Support up to 150MHz input data

- MIPI CSI RX Interface

- Compatible with the MIPI Alliance Interface specification 2

- Up to 4 data lane, 2.0Gbps maximum data rate per lane

- Support MIPI-HS, MIPI-LP mode

- VIP

- Support BT601 YCbCr 422 8-bit input

- Support BT656 YCbCr 422 8-bit input

- Support UYVY/VYUY/YUYV/YVYU configurable

- Support RAW 8/10/12-bit input

- Support JPEG input

- Support BT1120 16-bit,single/dual-edge sampling

- Support receiving CSI2 protocol data(up to four IDs)

- Support receiving DSI protocol data(Video mode/Command mode)

- Support window cropping

- Support virtual stride when write to DDR

- Support different stored address for Y and UV

- Support 422/420 output

- Support the polarity of pixel_clk、hsync、vsync configurable

- ISP supports the following features:

- Input interface

- DVP interface

- ITU-R BT601/656 with raw8/raw10/raw12

- MIPI interface

- Support x1/x2/x4 DPHY RX data lanes

- Support RAW8, RAW10, RAW12

- Maximum input resolution is 1920×1080

- ISP process

- Support Black level compensation

- Support 4 channels of Lens shade correction

- Support AF/AWB/AE/Hist

- Support Defect pixel cluster correction

- Support De-noising pre filter

- Support LP for Green Imbalance Correction

- Support Chromatic aberration correction

- Support Combined edge sensitive Sharpening/Blurring filter

- Support Color correction matrix

- Support color processing (contrast, saturation, brightness, hue, offset, range)

- Support Digital image effects (Emboss, Sketch, Sepia, Grayscale, Color Selection, Negative image, sharpening)

- Support Main/Self scaler up and down

- Output interface

- YUV422sp/YUV420sp, with UV swap

- RGB888/RGB666/RGB565

- RAW 8-bit/RAW 12-bit

- Bus interface

- Support 32-bit AHB programming interface

- Support AXI 128-bit interface

- Support 128-bit MMU

- Interrupt

- frame end, capture error, data loss

- Input interface

1.2.10 Display interface

- Parallel output interface

- Up to 1280×800@60fps display output

- Maximum with 18-bit output data

- Compatible with RGB and MCU mode

- MIPI DSI interface

- Compatible with MIPI Alliance Interface specification 2

- Support 4 data lane, 2.0Gbps maximum data rate per lane

- Up to 1080p@60fps display output

1.2.11 Video Output Processor LITE(VOP_LITE)

- Display interface

- Parallel output Interface:18-bit(RGB666), 16-bit(RGB565)

- MIPI DSI interface

- Max output resolution

- 1920×1080 for MIPI

- 1280×800 for RGB

- Display process

- Background layer

- programmable 24-bit color

- Win1 layer

- RGB888, ARGB888, RGB565

- Background layer

- Support virtual display

- 256 level alpha blending (pre-multiplied alpha support)

- Transparency color key

- Others

- Support dither down allegro RGB888to666 and RGB888to565

- Support dither down frc (configurable) RGB888to666

- Blank and black display

- Standby mode

- Support DMA stop mode

1.2.12 Video Output Processor RAW(VOP_RAW)

- Data interface

- RGB data channel

- pdaf data channel

- Max resolution:16M pixel data

- Layer process

- Background layer

- Programmable 10-bit raw

- Win layer

- Support data format : RAW8/RAW10/RAW16

- Support virtual display

- Others

- Support ping-pong mode

- PDAF support Hblank/Vblank/interleave mode

- Background layer

1.2.13 Audio Interface

- I2S0 with 8 channel

- Up to 8 channels TX and 8 channels RX path

- Audio resolution from 16bits to 32bits

- Sample rate up to 192KHz

- Provides master and slave work mode, software configurable

- Support 3 I2S formats (normal, left-justified, right-justified)

- Support 4 PCM formats (early, late1, late2, late3)

- Support configured as I2S mode or PCM mode

- Support TDM normal, 1/2 cycle left shift, 1 cycle left shift, 2 cycle left shift, right shift mode serial audio data

- I2S1 with 2 channel

- Up to 2 channels for TX and 2 channels RX path

- Audio resolution from 16bits to 32bits

- Sample rate up to 192KHz

- Provides master and slave work mode, software configurable

- Support 3 I2S formats (normal, left-justified, right-justified)

- Support 4 PCM formats (early, late1, late2, late3)

- Support configured as I2S mode or PCM mode

- PDM

- Up to 8 channels

- Audio resolution from 16bits to 24bits

- Sample rate up to 192KHz

- Support PDM master receive mode

- Voice Activity Detection(VAD)

- Support read voice data from I2S/PDM

- Support voice amplitude detection

- Support Multi-Mic array data storing

- Support a level combined interrupt

1.2.14 Connectivity

- SDIO interface

- Compatible with SDIO3.0 protocol

- 4bits data bus widths

- GMAC 10/100/1000M Ethernet controller

- Supports 10/100/1000-Mbps RGMII interfaces and 10/100-Mbps RMII interface

- Supports both full-duplex and half-duplex operation

- Supports CSMA/CD Protocol for half-duplex operation

- Supports packet bursting and frame extension in 1000 Mbps half-duplex operation

- Supports IEEE 802.3x flow control for full-duplex operation

- Preamble and start-of-frame data (SFD) insertion in Transmit, and deletion in receive paths

- Automatic CRC and pad generation controllable on a per-frame basis

- Options for Automatic Pad/CRC Stripping on receive frames

- Programmable fame length to support Standard Ethernet frames

- Supports IEEE 802.1Q VLAN tag detection for reception frames

- Support detection of LAN wake-up frames and AMD Magic Packet frames

- MDIO Master interface for PHY device configuration and management

- Support detection of LAN wake-up frames and AMD Magic Packet frames

- USB 2.0 Host

- Compatible with USB 2.0 specification

- Supports high-speed(480Mbps), full-speed(12Mbps) and low-speed(1.5Mbps) mode

- Support Enhanced Host Controller Interface Specification (EHCI), Revision 0

- Support Open Host Controller Interface Specification (OHCI), Revision 0a

- USB 2.0 OTG

- Compatible with USB2.0 specification

- Supports high-speed(480Mbps), full-speed(12Mbps) and low-speed (1.5Mbps mode)

- USB 0

- Compatible with USB3.0 Specification

- Universal Serial Bus 3.0 Specification, Revision 0

- Universal Serial Bus Specification, Revision 0

- Extensible Host Controller Interface for Universal Serial Bus (xHCI), Revision 1.1

- Support Control/Bulk (including stream)/Interrupt/Isochronous Transfer

- Supports super-speed (5Gbps)

- Descriptor Caching and Data Pre-fetching

- Doesn’t include USB2.0, it needs to be combined with USB2.0 OTG to form a complete USB3.0

- Compatible with USB3.0 Specification

- PCIe interface②

- Compatible with PCI Express Base Specification Revision 1

- Dual operation mode: Root Complex(RC)and End Point(EP)

- Maximum link width is 2, single bi-directional Link interface

- Maximum Payload Size of 128 bytes

- Support 2.5Gbps and 5.0Gbps serial data transmission rate per lane per direction

- SPI interface (Shared Peripheral Interrupts)

- Support 2 SPI Controllers(SPI1/SPI2), one support one chip-select output and the other support two chip-select output

- Support serial-master and serial-slave mode, software-configurable

- SPI2APB interface(SPI0)

- Support slave mode SPI protocol

- Support serial-slave mode only

- Support accessing internal address space by SPI slave interface

- I2C interface

- Support 6 I2C interfaces(I2C0-I2C5)

- Support 7bits and 10bits address mode

- Software programmable clock frequency

- Data on the I2C-bus can be transferred at rates of up to 100KHz in the Standard- mode, up to 400KHz in the Fast-mode or up to 1MHz in Fast-mode

- UART interface

- Support 8 UART interfaces(UART0-UART7)

- Support different input clock for UART operation to get up to 4Mbps baud rate

- Support auto flow control mode for UART0/UART1/UART3/UART4/UART5

1.2.15 Others

- Multiple group of GPIO

- All of GPIOs can be used to generate interrupt

- Support level trigger and edge trigger interrupt

- Support configurable polarity of level trigger interrupt

- Support configurable rising edge, falling edge and both edge trigger interrupt

- Support configurable pull direction (a weak pull-up and a weak pull-down)

- Support configurable drive strength

- Temperature sensor(TSADC)

- -40~125℃ temperature range and 5℃ temperature resolution

- Successive approximation ADC (SARADC)

- 10-bit resolution

- Up to 1Msps sampling rate

- 4 single-ended input channels

- eFUSE

- Support 2K bits Size, 1K bits for secure application, the other for non-secure

- Support Program/Read/Idle mode

- Package type

FCCSP 420-pin (body: 14mm x 14mm; ball size: 0.3mm; ball pitch: 0.70/0.35mm(inline/stagger))