1.1 Overview

1.1 Overview

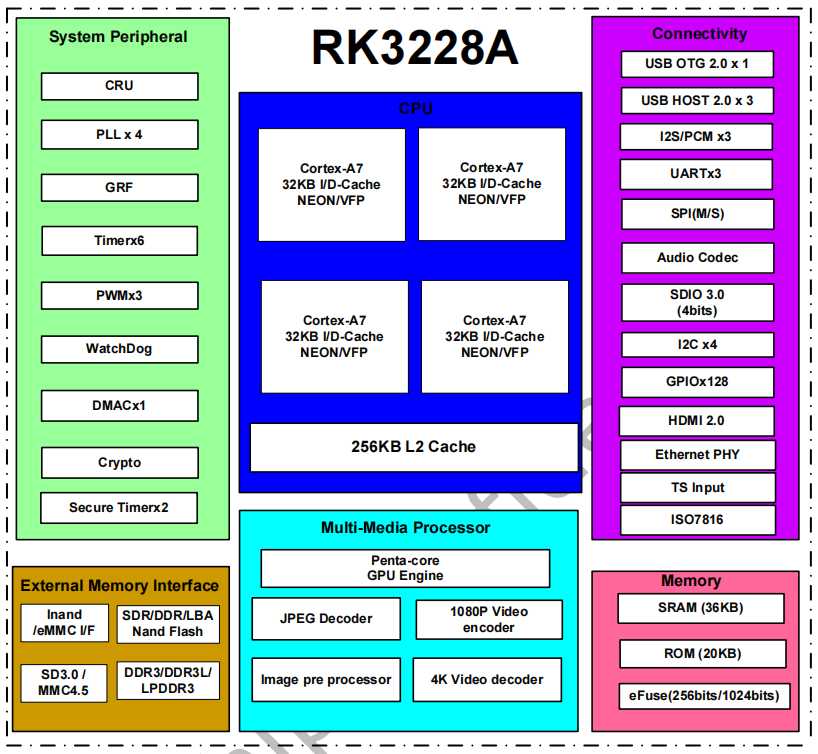

RK3228A is a high performance Quad-core application processor for smart TV-Box. Especially it is a high-integration and cost efficient SOC for 4K H.265/H.264 TV-Box. Quad-core Cortex-A7 is integrates with separately Neon and FPU coprocessor, also shared 256KB L2 Cache. The penta-core GPU including one geometry processors (GP) and dual pixel processors (PP) and dual core 2D GPU engine, support smoothly high-resolution display and mainstream game.

Lots of high-performance interface to get very flexible solution, such as multi-pipe display with HDMI2.0, TV Encoder is integrated for support security BOOT. 32bits DDR3/LPDDR3 provides high memory bandwidths for high-performance.

1.2 Features

The features listed below which may or may not be present in actual product, may be subject to the third party licensing requirements. Please contact Rockchip for actual product feature configurations and licensing requirements.

1.2.1 Microprocessor

Quad-core ARM Cortex-A7MP Core processor, a high-performance, low-power and cached application processor

Full implementation of the ARM architecture v7-A instruction set, ARM Neon Advanced SIMD (single instruction, multiple data) support for accelerated media and signal processing computation

Separately Integrated Neon and FPU per CPU

32KB/32KB L1 I-Cache/D-Cache per CPU.

Unified 256KB L2 Cache.

1.2.2 Memory Organization

Internal on-chip memory

BootRom

Internal SRAM

External off-chip memory①

DDR3/DDR3L/LPDDR2/LPDDR3

Async/Toggle/SyncNand Flash(include LBA Nand)

1.2.3 Internal Memory

Internal BootRom

Size : 20KB

Support system boot from the following device :

8bits Async Nand Flash

8bits toggle Nand Flash

SPI interface

eMMC interface

SDMMC interface

Support system code download by the following interface:

USB OTG interface

Internal SRAM

Size : 36KB

1.2.4 External Memory or Storage device

Dynamic Memory Interface (DDR3/DDR3L/LPDDR2/LPDDR3)

RK3228A Datasheet Rev 1.1

Compatible with JEDEC standard DDR3-1600/DDR3L-1600/LPDDR2-800/LPDDR3-1333 SDRAM

Supports 32 Bits data width, 2 ranks (chip selects), totally 2GB (max) address space.

Programmable timing parameters to support DDR3/DDR3L/LPDDR2/LPDDR3 SDRAM from various vendor

Advanced command reordering and scheduling to maximize bus utilization

Low power modes, such as power-down and self-refresh for DDR3/LPDDR2/LPDDR3 SDRAM; clock stop and deep power-down for LPDDR2 SDRAM

Compensation for board delays and variable latencies through programmable pipelines

Programmable output and ODT impedance with dynamic PVT compensation

Nand Flash Interface

Support 8bits async/toggle/sync nandflash, up to 4 banks

Support LBA nandflash

16bits, 24bits, 40bits, 60bits hardware ECC

For DDR nandflash, support DLL bypass and 1/4 or 1/8 clock adjust

For async/toggle nandflash, support configurable interface timing,

maximum data rate is 16bit/cycle

Embedded AHB master interface to do data transfer by DMA method

eMMC Interface

Compatible with standard iNAND interface

Support MMC4.51 protocol

Provide eMMC boot sequence to receive boot data from external eMMC device

Support FIFO over-run and under-run prevention by stopping card clock automatically

Support CRC generation and error detection

Embedded clock frequency division control to provide programmable baud rate

Support block size from 1 to 65535Bytes

8bits data bus width

SD/MMC Interface

Compatible with SD3.0, MMC ver4.51

Support FIFO over-run and under-run prevention by stopping card clock automatically

Support CRC generation and error detection

Support block size from 1 to 65535Bytes

Data bus width is 4bits

1.2.5 System Component

CRU (clock & reset unit)

Support clock gating control for individual components inside RK3228A

One oscillator with 24MHz clock input and 4 embedded PLLs

Support global soft-reset control for whole SOC, also individual soft-reset for every components

Timer

6 on-chip 64bits Timers in SoC with interrupt-based operation for non-secure application

2 on-chip 64bits Timers in SoC with interrupt-based operation for secure application

Provide two operation modes: free-running and user-defined count

Support timer work state checkable

Fixed 24MHz clock input

PWM

Four on-chip PWMs with interrupt-based operation

Programmable pre-scaled operation to bus clock and then further scaled

Embedded 32-bit timer/counter facility

RK3228A Datasheet Rev 1.1

Support capture mode

Support continuous mode or one-shot mode

Provides reference mode and output various duty-cycle waveform

WatchDog

32 bits watchdog counter width

Counter clock is from apb bus clock

Counter counts down from a preset value to 0 to indicate the occurrence of a timeout

WDT can perform two types of operations when timeout occurs:

Generate a system reset

First generate an interrupt and if this is not cleared by the service routine by the time a second timeout occurs then generate a system reset

Programmable reset pulse length

Totally 16 defined-ranges of main timeout period

Bus Architecture

128bit/64-bit/32-bit multi-layer AXI/AHB/APB composite bus architecture

5 embedded AXI interconnect

CPU interconnect with four 64-bits AXI masters, one 64-bits AXI slaves, one 32-bits AHB master and lots of 32-bits AHB/APB slaves

PERI interconnect with two 64-bits AXI masters, one 64-bits AXI slave, five 32-bits AHB masters and lots of 32-bits AHB/APB slaves

Display interconnect with three 128-bits AXI master, four 64-bits AXI masters and one 32-bits AHB slave

GPU interconnect with one 128-bits AXI master with point-to-point AXI-litearchitecture and 32-bits APB slave

VCODEC interconnect also with two 64-bits AXI master and two 32-bits AHB slave,they are point-to-point AXI-lite architecture

Flexible different QoS solution to improve the utility of bus bandwidth

Interrupt Controller

Support 3 PPI interrupt source and 128 SPI interrupt sources input from different components inside RK3228A

Support 16 software-triggered interrupts

Input interrupt level is fixed , only high-level sensitive

Two interrupt outputs (nFIQ and nIRQ)separately for each Cortex-A7, both are low-level sensitive

Support different interrupt priority for each interrupt source, and they are always software-programmable

DMAC

Micro-code programming based DMA

The specific instruction set provides flexibility for programming DMA transfers

Linked list DMA function is supported to complete scatter-gather transfer

Support internal instruction cache

Embedded DMA manager thread

Support data transfer types with memory-to-memory, memory-to-peripheral,peripheral-to-memory

Signals the occurrence of various DMA events using the interrupt output signals

Mapping relationship between each channel and different interrupt outputs is software-programmable

One embedded DMA controller for system

DMAC features:

8 channels totally

16 hardware request from peripherals

2 interrupt output

Dual APB slave interface for register configuration, designated as secure and non-secure

1.2.6 Video CODEC

Embedded memory management unit(MMU)

Video Decoder

Real-time video decoder of MPEG-1, MPEG-2, MPEG-4,H.263, H.264, H.265,VC-1,VP8, MVC

MMU Embedded

Supports frame timeout interrupt , frame finish interrupt and bitstream error interrupt

Error detection and concealment support for all video formats

Output data format YUV420 semi-planar,YUV400(monochrome) ,YUV422 is supported by H.264

H.264 8bit up to HP level 5.1 : 2160P@60fps (4096×2304)

HEVC 8bit: 2160p @60fps(4096×2304)

MPEG-4 up to ASP level 5 : 1080p@60fps (1920×1088)

MPEG-2 up to MP : 1080p@60fps (1920×1088)

MPEG-1 up to MP : 1080p@60fps (1920×1088)

H.263 : 576p@60fps (720×576)

VC-1 up to AP level 3 : 1080p@30fps (1920×1088)

VP8 : 1080p@60fps (1920×1088)

MVC : 1080p@60fps (1920×1088)

For H.264, image cropping not supported

For MPEG-4, GMC(global motion compensation) not supported

For VC-1, upscaling and range mapping are supported in image post-processor

For MPEG-4 SP/H.263, using a modified H.264 in-loop filter to implement deblocking filter in post-processor unit

Video Encoder

Support video encoder for H.264 UP to HP@level4.1, MVC

Only support I and P slices, not B slices

Support error resilience based on constrained intra prediction and slices

Input data format:

YCbCr 4:2:0 planar

YCbCr 4:2:0 semi-planar

YCbYCr 4:2:2

CbYCrY 4:2:2 interleaved

RGB444 and BGR444

RGB555 and BGR555

RGB565 and BGR565

RGB888 and BRG888

RGB101010 and BRG101010

Image size is from 96×96 to 1920×1080(Full HD)

Maximum frame rate is up to 1920×1080 @ 30FPS②

1.2.7 JPEG CODEC

JPEG decoder

Input JPEG file : YCbCr 4:0:0, 4:2:0, 4:2:2, 4:4:0, 4:1:1 and 4:4:4 sampling formats

Output raw image : YCbCr 4:0:0, 4:2:0, 4:2:2, 4:4:0, 4:1:1 and 4:4:4 semi-planar

Decoder size is from 48×48 to 8176×8176(66.8Mpixels)

Support JPEG ROI(region of image) decode

Maximum data rate③ is up to 76million pixels per second

Embedded memory management unit(MMU)

1.2.8 Image Enhancement (IEP module)

Image format support

RK3228A Datasheet Rev 1.1

Input data: YUV420/YUV422

Output data: YUV420/YUV422

YUV swap

UV SP/P

BT601_l/BT601_f/BT709_l/BT709_f color space conversion

YUV up/down sampling

De-interlace

3×5 Y motion detection matrix

Source width up to 1920

Configured high frequency de-interlace

I4O2 (Input 4 field, output 2 frame) /I4O1B/I4O1T/I2O1B/I2O1T mode

Interface

32bit AHB bus slave

64bit AXI bus master

Combined interrupt output

1.2.9 Graphics Engine

RK3228A’s GPU consists of penta-core that is tri-core 3D Graphics engine and dual-core 2D Graphics engine.

Tri-Core 3D Graphics Engine :

High performance OpenGL ES1.1 and 2.0, OpenVG1.1 etc.

Embedded 2 shader cores with shared hierarchical tiler

Separate vertex(geometry) and fragment(pixel) processing for maximum parallel throughput

Provide MMU and L2 Cache with 64KB size

Dual-Core 2D Graphics Engine:

Source formats :

ABGR8888, XBGR888, ARGB8888, XRGB888

RGB888, RGB565

RGBA5551, RGBA4444

YUV420 planar, YUV420 semi-planar

YUV422 planar, YUV422 semi-planar

YUV 10-bit for YUV420/422 semi-planar

BPP8, BPP4, BPP2, BPP1

Destination formats :

ABGR8888, XBGR888, ARGB8888, XRGB888

RGB888, RGB565

RGBA5551, RGBA4444

YUV420 planar, YUV420 semi-planar

YUV422 planar, YUV422 semi-planar

Pixel Format conversion, BT.601/BT.709

Max resolution: 8192×8192 source, 4096×4096 destination

BitBLT

Two source BitBLT:

A+B=B only BitBLT, A support rotate&scale when B fixed

A+B=C second source (B) has same attribute with (C) plus rotation function

Color fill with gradient fill, and pattern fill

High-performance stretch and shrink

Monochrome expansion for text rendering

New comprehensive per-pixel alpha(color/alpha channel separately)

Alpha blending modes including Java 2 Porter-Duff compositing blending rules ,chroma key, pattern mask, fading

Dither operation

0, 90, 180, 270 degree rotation

x-mirror, y-mirror & rotation operation

RK3228A Datasheet Rev 1.1

1.2.10 Video OUT

Display Interface

Support HDMI 2.0 output up to 4K@60Hz

TV Interface: TV encoder 10bit out for DAC

HDMI Interface : 24 bit(RGB888 YCbCr444), 30 bit(RGB101010,YCbCr 420, YCbCr 444)

Max output resolution 4K for HDMI, 480i/576i for CVBS

3 display layers :

Display layers of Win0,Win1,HWC

One background layer with programmable 24bits color

One video layer (win0/win1)

RGB888, ARGB888, RGB565, YCbCr422, YCbCr420, YCbCr444,YCbCr 420 10bit,YCbCr 422 10bit,YCbCr 444 10bit

maximum resolution is 4096×2304,support virtual display

1/8 to 8 scaling up/down engine with arbitrary non-integer ratio

256 level alpha blending(pre-multiplied alpha support)

Support transparency color key

Support BG, RG, RB swap, xy mirror

Support TV Encoder for PAL and NTSC

YCbCr2RGB(rec601-mpeg/rec601-jpeg/rec709)

YCbCr2RGB(BT2020)

RGB2YCbCr(BT601/BT709)

RGB2YCbCr(BT2020)

BT2020 and BT709/601 conversion

Win0 and Win1 layer overlay exchangeable

Support replication(16bits to 24bits) and dithering(24bits to 16bits/ 18bits) operation

Blank and blank display

1.2.11 HDMI

Support YUV420 4k x 2k @ 60fps

Support for 4k x 2k and 3D video formats

Support for up to 10.2bps bandwidth

HPD input analog comparator

Compliant HDMI 2.0

Compliance HDMI compliance Test specification 1.4

Support HDCP 2.2

1.2.12 Audio Interface

I2S0/I2S1 with 8ch

I2S0/I2S1 supports up to 8 channels (8xTX or 8xRX)

Audio resolution from 16bits to 32bits

Sample rate up to 192KHz

Provides master and slave work mode, software configurable

Support 3 I2S formats (normal, left-justified, right-justified)

Support 4 PCM formats(early, late1, late2, late3)

I2S and PCM mode cannot be used at the same time

I2S2/PCM with 2ch

Up to 2 channels (2xTX and 2xRX)

Audio resolution from 16bits to 32bits

Sample rate up to 192KHz

Provides master and slave work mode, software configurable

Support 3 I2S formats (normal , left-justified , right-justified)

Support 4 PCM formats(early , late1 , late2 , late3)

I2S and PCM cannot be used at the same time

RK3228A Datasheet Rev 1.1

SPDIF

Support two 16-bit audio data store together in one 32-bit wide location

Support biphase format stereo audio data output

Support 16 to 31 bit audio data left or right justified in 32-bit wide sample data buffer

Support 16, 20, 24 bits audio data transfer in linear PCM mode

Support non-linear PCM transfer

Audio CODEC

24bit DAC

Support Line-out

Support Mono, Stereo, 5.1 HiFi channel performance

Integrated digital interpolation and decimation filter.

Sampling rate of 8kHz/12kHz/16kHz/24kHz/32kHz/44.1KHz/48KHz/96KHz

Optional fractional PLL available that support 6MHz to 20MHz clock input to any clock

1.2.13 Connectivity

SDIO interface

Compatible with SDIO 3.0 protocol

4bits data bus widths

TS interface

Supports one TS input channels.

Supports 4 TS Input Mode: sync/valid mode in the case of serial TS input;nosync/valid mode, sync/valid, sync/burst mode in the case of parallel TS input.

Supports 2 TS sources: demodulators and local memory.

Supports 2 Built-in PTIs(Programmable Transport Interface) to process TS simultaneously, and Each PTI supports:

64 PID filters.

TS descrambling with 16 sets of Control Word under CSA v2.0 standard, up to 104Mbps

16 PES/ES filters with PTS/DTS extraction and ES start code detection.

4/8 PCR extraction channels

64 Section filters with CRC check, and three interrupt mode: stop per unit,full-stop, recycle mode with version number check

PID done and error interrupts for each channel

PCR/DTS/PTS extraction interrupt for each channel

Supports 1 PVR(Personal Video Recording) output channel.

1 built-in multi-channel DMA Controller.

Smart Card

support card activation and deactivation

support cold/warm reset

support Answer to Reset (ATR) response reception

support T0 for asynchronous half-duplex character transmission

support T1 for asynchronous half-duplex block transmission

support automatic operating voltage class selection

support adjustable clock rate and bit (baud) rate

support configurable automatic byte repetition

GMAC 10/100/1000M Ethernet Controller

Supports 10/100/1000-Mbps data transfer rates with the RGMII interfaces

Supports 10/100-Mbps data transfer rates with the RMII interfaces

Supports both full-duplex and half-duplex operation

Supports CSMA/CD Protocol for half-duplex operation

Supports packet bursting and frame extension in 1000 Mbps half-duplex operation

RK3228A Datasheet Rev 1.1

Supports IEEE 802.3x flow control for full-duplex operation

Optional forwarding of received pause control frames to the user application in full-duplex operation

Back-pressure support for half-duplex operation

Automatic transmission of zero-quanta pause frame on deassertion of flow control

input in full-duplex operation

Preamble and start-of-frame data (SFD) insertion in Transmit, and deletion in Receive paths

Automatic CRC and pad generation controllable on a per-frame basis

Options for Automatic Pad/CRC Stripping on receive frames

Programmable Inter-Frame-Gap (40-96 bit times in steps of 8)

Supports a variety of flexible address filtering modes

Separate 32-bit status returned for transmission and reception packets

Supports IEEE 802.1Q VLAN tag detection for reception frames

Support detection of LAN wake-up frames and AMD Magic Packet frames

Support checksum off-load for received IPv4 and TCP packets encapsulated by the Ethernet frame

Support checking IPv4 header checksum and TCP, UDP, or ICMP checksum encapsulated in IPv4 or IPv6 datagram

Comprehensive status reporting for normal operation and transfers with errors

Automatic generation of PAUSE frame control or backpressure signal to the GMAC core based on Receive FIFO-fill (threshold configurable) level

Handles automatic retransmission of Collision frames for transmission

Discards frames on late collision, excessive collisions, excessive deferral and under-run conditions

Ethernet PHY

Integrated IEEE 802.3/802.3u compliant 10/100Mbps Ethernet PHY

Supporting both full and half duplex for either 10 or 100 Mb/s data rate

Auto MDIX capable

Supports wake-on-LAN, EEE

100Base-FX support

MII/RMII interface

Supports auto-negotiation

On-board diagnosis

SPI Controller

Support serial-master and serial-slave mode, software-configurable

DMA-based or interrupt-based operation

Embedded two 32x16bits FIFO for TX and RX operation respectively

Support 2 chip-selects output in serial-master mode

UART Controller

3 on-chip UART controller inside RK3228A

DMA-based or interrupt-based operation

UART0/1/2 Embedded two 64Bytes FIFO for TX and RX operation respectively

Support 5bit,6bit,7bit,8bit serial data transmit or receive

Standard asynchronous communication bits such as start, stop and parity

Support different input clock for UART operation to get up to 4Mbps or other special baud rate

Support non-integer clock divides for baud clock generation

Support auto flow control mode

I2C controller

4 on-chip I2C controller in RK3228A

Multi-master I2C operation

Support 7bits and 10bits address mode

RK3228A Datasheet Rev 1.1

Software programmable clock frequency and transfer rate up to 400Kbit/s in the fast mode

Serial 8bits oriented and bidirectional data transfers can be made at up to 100Kbit/s in the standard mode

GPIO

4 groups of GPIO (GPIO0~GPIO3) , 32 GPIOs per group in GPIO0~GPIO3, totally have 128 GPIOs

All of GPIOs can be used to generate interrupt to Cortex-A7

All of pull-up GPIOs are software-programmable for pull-up resistor or not

All of pull-down GPIOs are software-programmable for pull-down resistor

or not

All of GPIOs are always in input direction in default after power-on-reset

USB Host2.0

Embedded 3 USB Host 2.0 interfaces

Compatible with USB Host2.0 specification

Supports high-speed(480Mbps), full-speed(12Mbps) and low-speed(1.5Mbps) mode

Provides 16 host mode channels

Support periodic out channel in host mode

USB OTG2.0

Compatible with USB OTG2.0 specification

Supports high-speed(480Mbps), full-speed(12Mbps) and low-speed(1.5Mbps) mode

Support up to 9 device mode endpoints in addition to control endpoint 0

Support up to 6 device mode IN endpoints including control endpoint 0

Endpoints 1/3/5/7 can be used only as data IN endpoint

Endpoints 2/4/6 can be used only as data OUT endpoint

Endpoints 8/9 can be used as data OUT and IN endpoint

Provides 9 host mode channels

1.2.14 Others

Temperature Sensor(TS-ADC)

10-bits SAR ADC up to 50KS/s sampling rate

0~80C temperature range and 5C temperature resolution

eFuse

Two high-density electrical Fuse is integrated: 256bits (32×8) / 1024bits (32×32)

Support standby mode

Provide inactive mode, VP must be 0V or Floating in this mode.

Package Type

BGA316 (body: 14mm x 14mm ; ball size : 0.3mm ; ball pitch : 0.65mm)

Notes :

① : DDR3/LPDDR2/LPDDR3 are not used simultaneously as well as async and sync ddrnand flash

②: Actual maximum frame rate will depend on the clock frequency and system bus performance

③: Actual maximum data rate will depend on the clock frequency and JPEG compression rate

Rockchip RK3228A Datasheet V1.1