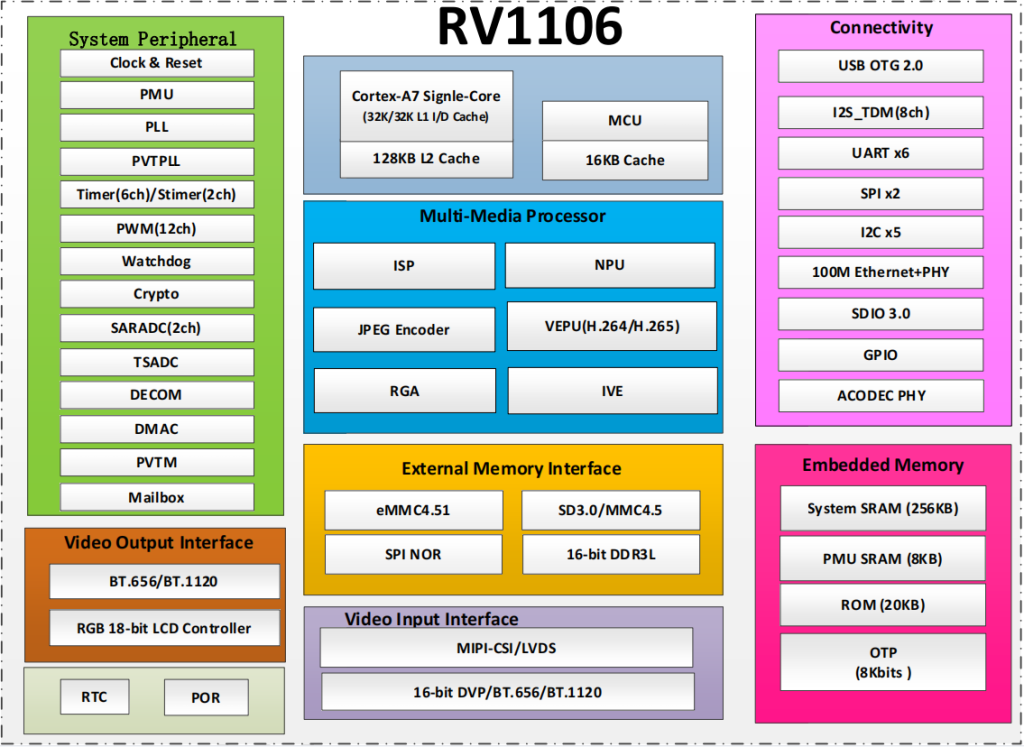

RV1106是瑞芯微旗下一款高度集成的ARM通用型SoC,主要面向IPC的机器视觉应用,性价比极高,适合大规模部署。RV1106基于单颗ARM Cortex-A7 32位CPU,集成了Neon和FPU。内置独立NPU,支持INT4/INT8/INT16混合操作,计算能力高达0.5TOPS。此外,凭借其强大的兼容性,可实现基于TensorFlow/MXNet/PyTorch/Caffe等一系列框架的网络模型转换。

RV1106推出了新一代完全基于硬件的最大500万像素ISP(图像信号处理器)。它实现了许多算法加速器,如HDR、3A、LSC、3DNR、2DNR、锐化、dehaze、gamma校正等。通过与两个MIPI CSI(或LVD)和一个DVP(BT.601/BT.656/BT.1120)接口的合作,用户可以构建一个同时接收来自3个摄像头传感器的视频数据的系统。

RV1106中嵌入的视频编码器支持H.265/H.264编码。它还支持多流编码。借助这一功能,来自摄像头的视频可以以更高的分辨率编码并存储在本地内存中,同时将另一个低分辨率视频传输到云存储。为了加速视频处理,还嵌入了一个带有22个计算单元的智能视频引擎。RV1106有一个内置的16位DRAM DDR3L,能够维持苛刻的内存带宽。它还集成了内置RTC、POR、音频编解码器和MAC物理层。

1.2.1 Application Processor

⚫ Single core ARM Cortex-A7

⚫ Full implementation of the ARM architecture v7-A instruction set, ARM Neon Advanced SIMD

⚫ Separately Integrated Neon and FPU

⚫ 32KB L1 I-Cache and 32KB L1 D-Cache

⚫ Unified 128KB L2 Cache for Cortex-A7

⚫ TrustZone technology support

⚫ One isolated voltage domain to support DVFS

1.2.2 Memory Organization

⚫ Internal on-chip memory

◼ BootRom

◆ Support system boot from the following device:

➢ SPI interface

➢ eMMC interface

➢ SD/MMC interface

◆ Support system code download by the following interface:

➢ USB interface

➢ UART interface

◼ 256KB Share Memory

◼ 8KB PMU SRAM

◼ RV1106G2 SIP 1Gb DDR3L

◼ RV1106G3 SIP 2Gb DDR3L

⚫ External off-chip memory

◼ eMMC Interface

◆ Fully compliant with JEDEC eMMC 4.51 specification

RV1106 Datasheet Rev 1.0

◆ Support HS200, but not support CMD Queue

◆ Support three data bus width: 1bit, 4bits or 8bits

◼ SD/MMC Interface

◆ Compatible with SD3.0, MMC ver4.51

◆ Data bus width is 4bits

◼ Flexible Serial Flash Interface (FSPI)

◆ Support transfer data from/to serial flash device

◆ Support 1bit, 2bits or 4bits data bus width

1.2.3 System Component

⚫ MCU

◼ MCU in VD_CORE integrate 16KB Cache

◼ Integrated Programmable Interrupt Controller, all IRQ lines connected to GIC for CPU also connect to MCU

◼ Integrated Debug Controller with JTAG interface

⚫ CRU (clock & reset unit)

◼ Support total 4 PLLs to generate all clocks

◼ One oscillator with 24MHz clock input

◼ Support clock gating control for individual components

◼ Support global soft-reset control for whole chip, also individual soft-reset for each component

⚫ PMU (power management unit)

◼ Multiple configurable work modes to save power by different frequency or automatic clock gating control or power domain on/off control

◼ Lots of wakeup sources in different mode

◼ Support 3 separate voltage domains,VDD_ARM,VDD_LOGIC,VDD_PMU.

⚫ Timer

◼ Support 2 secure timers with 64bits counter and interrupt-based operation

◼ Support 6 non-secure timers with 64bits counter and interrupt-based operation

◼ Support two operation modes: free-running and user-defined count for each timer

◼ Support timer work state checkable

⚫ PWM

◼ Support 12 on-chip PWMs (PWM0~PWM11) with interrupt-based operation

◼ Programmable pre-scaled operation to bus clock and then further scaled

◼ Embedded 32-bit timer/counter facility

◼ Support capture mode

◼ Support continuous mode or one-shot mode

◼ Provides reference mode and output various duty-cycle waveform

◼ Optimized for IR application for PWM3, PWM7, PWM11

⚫ Watchdog

◼ 32-bit watchdog counter

◼ Counter counts down from a preset value to 0 to indicate the occurrence of a timeout

◼ WDT can perform two types of operations when timeout occurs:

◆ Generate a system reset

◆ First generate an interrupt and if this is not cleared by the service routine by the time a second timeout occurs then generate a system reset

◼ One Watchdog for non-secure application

◼ One Watchdog for secure application

⚫ Interrupt Controller

◼ Support 121 SPI interrupt sources input from different components inside RV1106

RV1106 Datasheet Rev 1.0

◼ Support 16 software-triggered interrupts

◼ Input interrupt level is fixed, high-level sensitive or rising edge sensitive

◼ Support different interrupt priority for each interrupt source, and they are always software-programmable

⚫ DMAC

◼ Micro-code programming-based DMA

◼ Linked list DMA function is supported to complete scatter-gather transfer

◼ Support data transfer types including memory-to-memory, memory-to-peripherals, peripherals-to-memory

◼ Totally three embedded DMA controllers for peripheral system

◼ Each DMAC features:

◆ Support 8 channels

◆ 32 hardware requests from peripherals

◆ 2 interrupt output

◆ Support TrustZone technology and programmable secure state for each DMA channel

⚫ Secure System

◼ Embedded one cipher engines

◆ Support Link List Item (LLI) DMA transfer

◆ Support SHA-1, SHA-256/224, MD5 with hardware padding

◆ Support HMAC of SHA-1, SHA-256, MD5 with hardware padding

◆ Support AES-128, AES-192, AES-256 encrypt and decrypt cipher

◆ Support DES and TDES cipher

◆ Support AES ECB/CBC/OFB/CFB/CTR/CTS/XTS/GCM/CBC-MAC/CMAC mode

◆ Support DES/TDES ECB/CBC/OFB/CFB mode

◆ Support up to 4096 bits PKA mathematical operations for RSA/ECC/SM2

◼ Support generating random numbers, one secure only engine, another one security configurable

◼ Support secure OTP

◼ Support secure debug

◼ Support secure OS

◼ Except CPU, the other masters in the SoC can also support security and non-security mode by software-programmable

◼ Some slave components in SoC can only be addressed by security master and the other slave components can be addressed by security master or non-security master by software-programmable

◼ System SRAM (share memory), part of space is addressed only in security mode

◼ External DDR space can be divided into 16 parts, each part can be software-programmable to be enabled by each master

⚫ Mailbox

◼ One Mailbox in SoC to service CPU and MCU communication

◼ Support four mailbox elements, each element includes one data word, one command word register and one flag bit that can represent one interrupt

◼ Provide 32 lock registers for software to use to indicate whether mailbox is occupied

⚫ Decompression

◼ Support for decompressing GZIP files

◼ Support for decompressing data in DEFLATE format

◼ Support for decompressing data in ZLIB format

◼ Support the limit size function of the decompressed data to prevent the memory from being maliciously destroyed during the decompression process

⚫ Real Time Clock (RTC)

RV1106 Datasheet Rev 1.0

◼ Provides year, month, day, weekday, hours, minutes, and seconds based on a 32.768 kHz crystal oscillator

◼ Support compensation for the second and hour count

◼ BCD representation of time, calendar and alarm

◼ 12- or 24-hour clock with AM and PM in 12-hour mode

◼ Interrupts are separately software maskable

◆ Alarm interrupt

◆ Periodic interrupt

◆ Chip power off interrupt

◆ Battery power atypical interrupt

1.2.4 Video CODEC

⚫ Video Encoder

◼ H.265/HEVC Main Profile, level 5.0

◼ H.264/AVC High Profile, level 5.0

◼ Support multi-channel encoding with performance up to 5-megapixel@30fps

◼ JPEG baseline, up to 4-megapixel @60fps in standalone mode, resolution up to 8192 x 8192

◼ Bitrate up to 60Mbps

◼ Six bit rate control modes (CBR, VBR, FIXQP, AVBR, QPMAP, and CVBR)

◼ Support YUV420 and YUV400 format input

◼ Intelligent encoding mode

◼ 8-area OSD

◼ YUV/RGB video source with crop, rotation and mirror

◼ Ultra-low delay encoding

1.2.5 Neural Process Unit

⚫ Neural network acceleration engine with processing performance up to 0.5 TOPS ⚫ Support integer 4, integer 8 and integer 16 operation

⚫ Support creating simple custom operators

⚫ Support deep learning frameworks: TensorFlow, Caffe, Tflite, Pytorch, Onnx NN, etc.

1.2.6 Rockchip Intelligent Video Engine (RKIVE)

⚫ GMM

◼ Support 1 to 5 gaussian model

⚫ BGM (base on codebook)

◼ Support 3 codebook model

⚫ Canny

◼ Staging buffer stride require 64 pixel align

◼ Support 3X3 and 5×5 template coefficient

⚫ CCL

◼ Support max to 254 connected regions

◼ Support 4-connected and 8-connected region

⚫ Stcorner

◼ Support max to 500 corner sort output

⚫ LK

◼ Support max to 500 corner input

◼ Support 1~4 optical flow layers

⚫ Integral

◼ Require all the buffer base is 16bytes align

⚫ LBP

◼ Support simple and absolute value comparison mode

⚫ Filter

◼ Support 3X3 and 5×5 mode

⚫ Sobel

◼ Support 3X3 and 5×5 mode

⚫ Morph

RV1106 Datasheet Rev 1.0

◼ Support eroding and dilating mode

⚫ Denoise Filter

◼ Support minimum/median/maximum 3 types filter

⚫ DMA

◼ Support direct copy mode

◼ Support interval copy mode

⚫ CSC

◼ Support rgb2yuv, yuv2rgb, rgb2hsv, yuv2hsv

◼ Support 601 and 709 format, full and limit range

⚫ Hist/eqhist

◼ Support hist only, eqhist only, hist + eqhist 3 types mode

⚫ Logic OP

◼ Support logic and, logic or, logic xor, add, sub, absolute difference

⚫ Mag and Ang

◼ Calculation of the image gradient magnitude and direction

⚫ Morph

◼ Support eroding and dilating mode

⚫ NCC

◼ Calculation of the image normalized cross-correlation

⚫ Cast

◼ Data linear transformation

⚫ Sad

◼ Support sad size is 4×4, 8×8 and 16×16

⚫ Threshold

◼ Convert grayscale into a binary image

⚫ Map

◼ Support 8bit to 8bit and 8bit to 16bit map operation

1.2.7 Graphics Engine

⚫ 2D Graphics Engine

◼ Input data:

◆ ARGB/RGB888/RGB565/RGB4444/RGB5551

◆ YUV420/YUV422/YVYU422/YVYU420/YUV422SP10bit/YUV420SP10bit

◼ Output data:

◆ ARGB/RGB888/RGB565/RGB4444/RGB5551

◆ YUV420/YUV422/YUV400/Y4/YVYU422/YVYU420

◼ Pixel Format conversion, BT.601/BT.709

◼ Dither operation

◼ Max resolution: 8192×8192 source, 4096×4096 destination

◼ Scaling

◆ Down-scaling: Average filter

◆ Up-scaling: Bi-cubic filter(source>2048 would use Bi-linear)

◆ Arbitrary non-integer scaling ratio, from 1/16 to 16

◼ Rotation

◆ 0, 90, 180, 270-degree rotation

◆ x-mirror, y-mirror

◆ Mirroring and rotation co-operation

◼ BitBLT

◆ Block transfer

◆ Color palette/Color fill, support with alpha

◆ Transparency mode (color keying/stencil test, specified value/value range)

◆ Two source BitBLT

◆ A+B=B only BitBLT, A support rotate & scale when B fixed

◆ A+B=C second source (B) has same attribute with (C) plus rotation function

◼ Alpha Blending

◆ Comprehensive per-pixel alpha(color/alpha channel separately)

◆ Fading

RV1106 Datasheet Rev 1.0

◆ Support SRC1(R2Y)+SRC0(YUV) -> DST(YUV)

◆ Support DST Full CSC convert for YUV2YUV

◼ OSD Automatic Inversion

◆ Supports OSD sources in ARGB8888/ARGB1555/ARGB444/ARGB2BPP format

◆ Support SRC0 and OSD overlay

◼ Support square mosaic patterns to cover rectangular mosaic areas

1.2.8 Video Input Interface

⚫ MIPI Interface

◼ Two MIPI CSI DPHY

◆ Each MIPI DPHY V1.2, 2lanes, 1.5Gbps per lane

◆ Support to combine 2 DPHY together to one 4lanes

⚫ DVP interface

◼ One 8/10/12/16-bit standard DVP interface, up to 100MHz input data

◼ Support BT.601/BT.656 and BT.1120 VI interface

◼ Support the polarity of pixel_clk, hsync, vsync configurable

1.2.9 Image Signal Processor

⚫ Video Capture (VICAP)

◼ Support BT601 YCbCr 422 8bit input, RAW 8/10/12bit input

◼ Support BT656 YCbCr 422 8bit progressive/interlace input

◼ Support BT1120 YCbCr 422 16bit progressive/interlace input, single/dual-edge sampling

◼ Support YUYV sequence configurable

◼ Support the polarity of hsync and vsync configurable

◼ Support receiving two interfaces of MIPI CSI /LVDS, up to four IDs for each interface

◼ Support five CSI data formats: RAW8/10/12/14, YUV422

◼ Support three modes of MIPI CSI HDR: virtual channel mode, identification code mode, line counter mode

◼ Support four LVDS data formats: RAW8/10/12, YUV422

◼ Support reducing frame rate

◼ Support window cropping

◼ Support RAW data through to ISP

◼ Support 8/16/32 times down-sampling for RAW data

◼ Support virtual stride when write to DDR

◼ Support NV16/NV12/YUV400/YUYV output format for YUV data

◼ Support compact/non-compact output format for RAW data

⚫ Maximum input: 3072×1728 (5M) @30fps

⚫ Minimum input: 256×256

⚫ 3A: Include Auto Enhance (AE)/Histogram, Auto Focus (AF), and Auto White Balance (AWB) statistics output

⚫ EXPANDER: Sensor expander

⚫ BLC: Black Level Correction

⚫ DPCC: Static/Dynamic Defect Pixel Cluster Correction

⚫ PDAF: Phase Detection Auto Focus

⚫ LSC: Lens Shading Correction

⚫ Bayer-2DNR: Spatial Bayer-raw Noise Reduction

⚫ Bayer-3DNR: Temporal Bayer-raw Noise Reduction

⚫ CAC: Chromatic Aberration Correction

⚫ HDR-MGE: 2-Frame Merge into High-Dynamic Range

⚫ HDR-DRC: HDR Dynamic Range Compression, Tone mapping

⚫ GIC: Green Imbalance Correction

⚫ DeBayer: Advanced Adaptive Demosaic

⚫ CCM/CSM: Color Correction Matrix, RGB2YUV, etc.

⚫ Gamma: Gamma out correction

⚫ Dehaze/Enhance: Automatic Dehaze and effect enhancement

RV1106 Datasheet Rev 1.0

⚫ 3DLUT: 3D-LUT Color Palette for Customer

⚫ LDCH: Lens Distortion Correction only in the Horizontal direction

⚫ YUV-2DNR: Spatial YUV Noise Reduction

⚫ Sharp: Image sharpening and boundary filtering

⚫ CMSK: Privacy cover and mask

⚫ Gain: Image local gain

⚫ Multi-sensor reuse ISP, 4 sensors for maximum

⚫ Bus interface: 32bit AHB configuration, 128bit AXI R/W

⚫ Low power, auto-gating for each block

⚫ MI R/W burst group to improve memory utilization

⚫ MI 3+2 path output, MP stepless scaling, SP/BP scaling under 1080p, MPDS/SPDS fixed 1/16 downscaling

1.2.10 Display interface

⚫ Parallel RGB LCD Interface: 18-bit (RGB666), 16-bit (RGB565)

⚫ Serial RGB LCD Interface

⚫ MCU LCD Interface

⚫ Max output resolution: 1280×720 for RGB/BT656/BT1120

1.2.11 Video Output Processor

⚫ Display process

◼ Background layer

◆ programmable 18-bit color

◼ Win1 layer

◆ RGB888, ARGB888, RGB565

◆ Support virtual display

◆ 256 level alpha blending (pre-multiplied alpha support)

◆ Transparency color key

◆ RGB2YCbCr (BT601/BT709)

⚫ Others

◼ Support RGB or YUV domain overlay

◼ BCSH (Brightness, Contrast, Saturation, Hue adjustment)

◼ BCSH: YCbCr2RGB (rec601-mpeg/ rec601-jpeg/rec709)

◼ BCSH: RGB2YCbCr (BT601/BT709)

◼ Support dither down allegro RGB888to666 RGB888to565 & dither down frc (configurable) RGB888to666

◼ Blank and black display

◼ Standby mode

◼ Support all layers reg_done separately

1.2.12 Audio Interface

⚫ I2S0 with 8 channels

◼ Up to 8 channels TX and 8 channels RX path

◼ Audio resolution from 16bits to 32bits

◼ Sample rate up to 192KHz

◼ Provides master and slave work mode, software configurable

◼ Support 3 I2S formats (normal, left-justified, right-justified)

◼ Support 4 PCM formats (early, late1, late2, late3)

⚫ Audio Codec

◼ Support two 24-bits ADC channels with 90dB SNR for stereo recording from microphone

◼ Support one 24-bits DAC channels with 90dB SNR for stereo playback

◼ Support differential and single-ended microphone or line input

◼ Sampling rate of 8KHz/12KHz/16KHz/24KHz/32KHz/44.1kHz/48KHz/96KHz

1.2.13 Connectivity

⚫ SDIO interface

RV1106 Datasheet Rev 1.0

◼ Compatible with SDIO3.0 protocol

◼ 4-bit data bus widths

⚫ MAC 10/100M Ethernet controller and embedded PHY

◼ Support one Ethernet controllers

◼ Support 10/100-Mbps data transfer rates with the RMII interfaces

◼ Support both full-duplex and half-duplex operation

⚫ USB 2.0

◼ Compatible with USB 2.0 specification

◼ Support one USB 2.0 Host/Device

◼ Supports high-speed(480Mbps), full-speed(12Mbps) and low-speed(1.5Mbps) mode

◼ Support Enhanced Host Controller Interface Specification (EHCI), Revision 1.0

◼ Support Open Host Controller Interface Specification (OHCI), Revision 1.0a

⚫ SPI interface

◼ Support 2 SPI Controllers (SPI0-SPI1)

◼ Support two chip-select output

◼ Support serial-master and serial-slave mode, software-configurable

⚫ I2C Master controller

◼ Support 5 I2C Master(I2C0-I2C4)

◼ Support 7bits and 10bits address mode

◼ Software programmable clock frequency

◼ Data on the I2C-bus can be transferred at rates of up to 100k bits/s in the Standard-mode, up to 400k bits/s in the Fast-mode

⚫ UART interface

◼ Support 6 UART interfaces (UART0-UART5)

◼ Embedded two 64-byte FIFO for TX and RX operation respectively

◼ Support 5bit, 6bit, 7bit, 8bit serial data transmit or receive

◼ Standard asynchronous communication bits such as start, stop and parity

◼ Support different input clock for UART operation to get up to 4Mbps baud rate

◼ Support auto flow control mode for all UART

1.2.14 Others

⚫ Multiple groups of GPIO

◼ All of GPIOs can be used to generate interrupt

◼ Support level trigger and edge trigger interrupt

◼ Support configurable polarity of level trigger interrupt

◼ Support configurable rising edge, falling edge and both edge trigger interrupt

◼ Support configurable pull direction (a weak pull-up and a weak pull-down)

◼ Support configurable drive strength

⚫ Temperature Sensor (TS-ADC)

◼ Support User-Defined Mode and Automatic Mode

◼ In User-Defined Mode, start_of_conversion can be controlled completely by software, and also can be generated by hardware.

◼ In Automatic Mode, the temperature of alarm (high/low temperature) interrupt can be configurable

◼ In Automatic Mode, the temperature of system reset can be configurable

◼ -40~125°C temperature range and 1°C temperature resolution

⚫ Successive approximation ADC (SARADC)

◼ 10-bit resolution

◼ Up to 1MS/s sampling rate

◼ 2 single-ended input channels

⚫ OTP

◼ Support 8K bits Size, 7K bits for secure application

◼ Support Program/Read/Idle mode

⚫ Package Type

◼ RoHS QFN128 (body: 12.3mm x 12.3mm pitch 0.35mm)

RV1106 Datasheet Rev 1.0