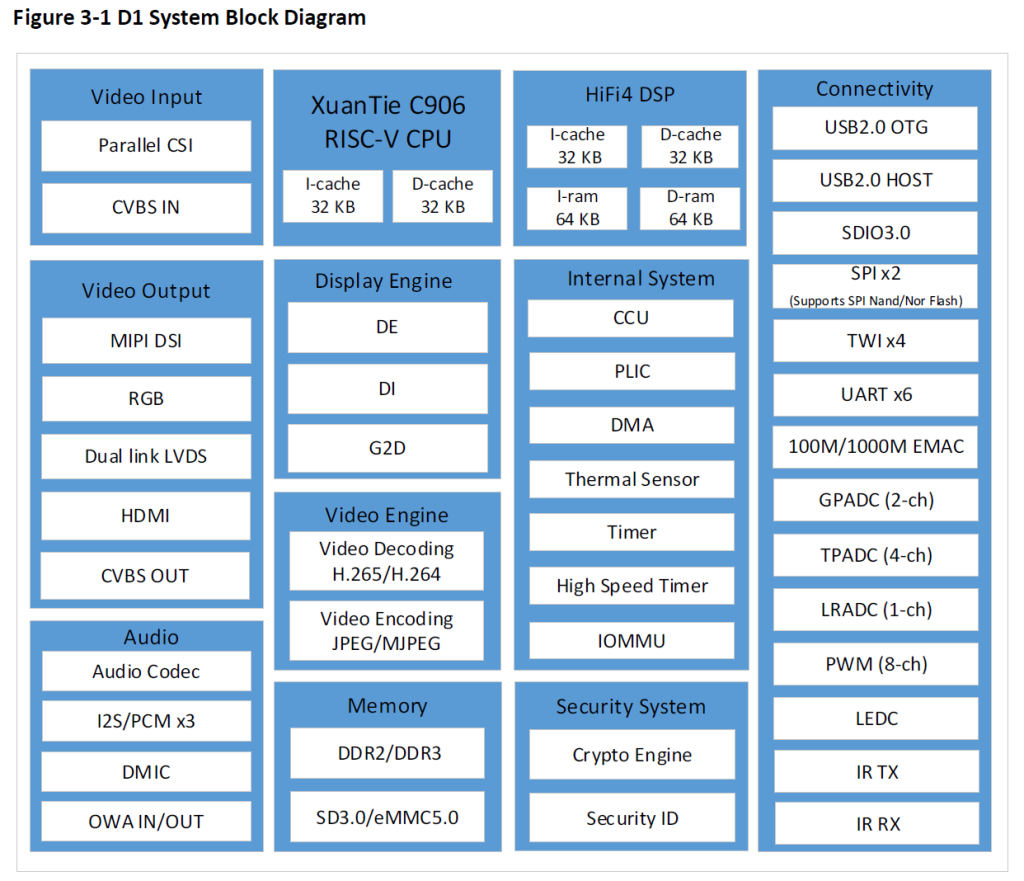

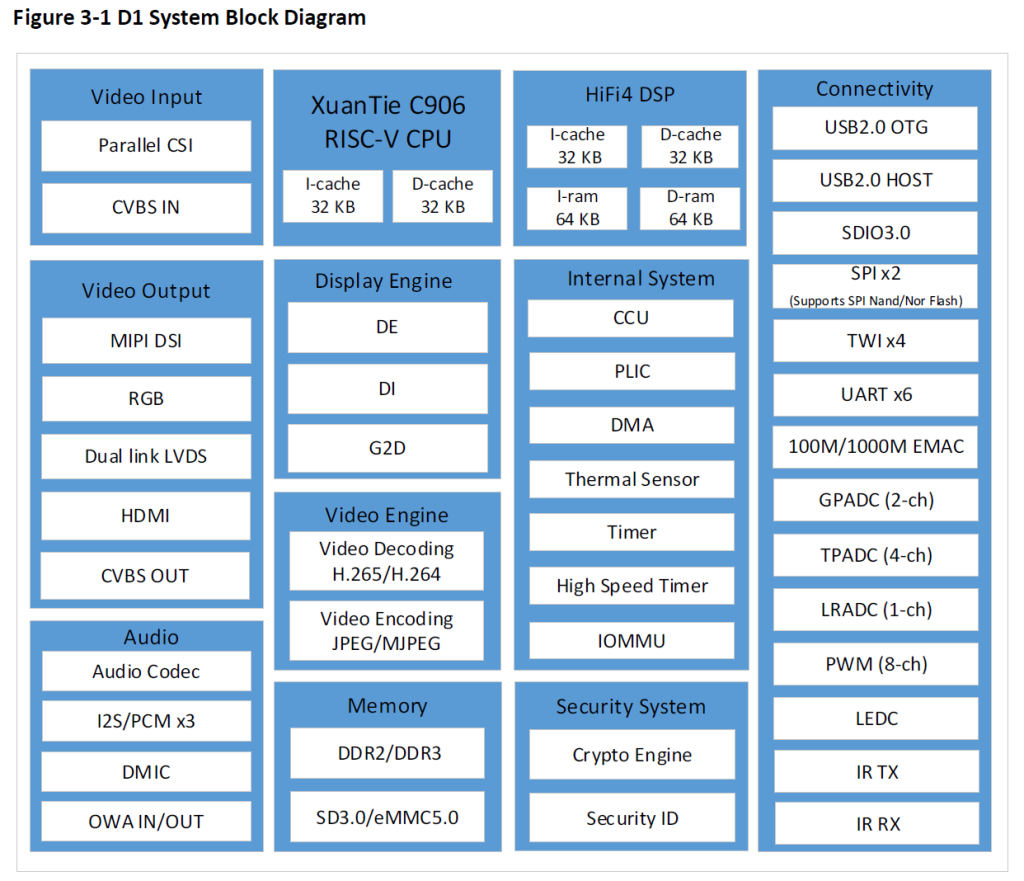

D1是为全志(Allwinner)基于RISC-V设计的高级应用SoC处理器。它集成了64位玄铁C906 RISC-V CPU和HiFi4 DSP,提供高效的计算能力。D1支持H.265、H.264、MPEG-1/2/4、JPEG、VC1等全格式解码。独立编码器可以用JPEG或MJPEG进行编码。集成的多ADC/DAC和I2S/PMC/DMIC/OWA音频接口可以与CPU无缝工作,以加速多媒体算法并改善用户体验。D1支持RGB/LVDS/MIPI DSI/HDMI/CVBS OUT显示输出接口,满足不同屏幕显示的要求。D1具有广泛的连接和接口,如USB、SDIO、EMAC、TWI、UART、SPI、PWM、GPADC、LRADC、TPADC、IR TX和RX等。此外,D1可以通过SDIO和UART与WiFi和BT等其他不同的外围设备连接。

FeaturesFeatures

2.1 CPU ArchitectureCPU Architecture

• XuanTie C906 RISC-V CPU

• 32 KB I32 KB I-cache + 32 KB Dcache + 32 KB D-cachecache

2.2 DSP ArchitectureDSP Architecture

• HiFi4HiFi4

• 32 KB L1 I32 KB L1 I-cache and 32 KB L1 Dcache and 32 KB L1 D-cache cache

• 64 KB I64 KB I-ram and 64 KB Dram and 64 KB D-ramram

2.3 Memory SubsystemMemory Subsystem

2.3.1 Boot ROM (BROM) Boot ROM (BROM)

• On -chip memorychip memory

• Supports system boot from the following devices:Supports system boot from the following devices:

– SD cardSD card

– eMMCeMMC

– SPI SPI NOR FlashNOR Flash

– SPI NAND FlashSPI NAND Flash

• Supports mandatory upgrade process through USBSupports mandatory upgrade process through USB and SD cardand SD card

• Supports GPIO pin Supports GPIO pin and eFuse module and eFuse module to select the boot media typeto select the boot media type

2.3.2 SDRAMSDRAM

• Supports DDR2/DDR3 SDRAMSupports DDR2/DDR3 SDRAM

• Maximum capacity up to 2 GBaximum capacity up to 2 GB

• Supports clock frequSupports clock frequency up to 533 MHz for DDR2ency up to 533 MHz for DDR2

• Supports clock frequency up to 800 MHz for DDR3Supports clock frequency up to 800 MHz for DDR3

2.3.3 SMHC SMHC

• Three SD/MMC host controller (SMHC) interfacesThree SD/MMC host controller (SMHC) interfaces

• The SMHC0 controls the devices that comply with the protocol Secure Digital Memory (SD memThe SMHC0 controls the devices that comply with the protocol Secure Digital Memory (SD mem-version version 3.0)3.0) Draft Version

• The SMHC1 controls the device that complies with The SMHC1 controls the device that complies with the protocol Secure Digital I/O (SDIOthe protocol Secure Digital I/O (SDIO-version 3.0)version 3.0)

• The SMHC2 controls the device that complies with the protocol Multimedia Card (eMMCThe SMHC2 controls the device that complies with the protocol Multimedia Card (eMMC-version 5.0)version 5.0)

• Maximum performance:Maximum performance:

– SDR mode 1SDR mode 150 MHz@1.8 V50 MHz@1.8 V IO pad IO pad

– DDR mode DDR mode 100 MHz@1.8 V100 MHz@1.8 V IO padIO pad

– DDR mode 50 MHz@3.3 V IO padDDR mode 50 MHz@3.3 V IO pad

• Supports 1Supports 1-bit or 4bit or 4-bit data widthbit data width

• Supports block size of 1 to 65535 bytesSupports block size of 1 to 65535 bytes

• Internal 1024Internal 1024-Bytes RX FIFO and 1024Bytes RX FIFO and 1024-Bytes TX FIFOBytes TX FIFO

• Supports cSupports card insertion and removal ard insertion and removal interruptinterrupt

• Supports hardSupports hardware CRC generation and error detectionware CRC generation and error detection

• Supports descriptorSupports descriptor-based internal DMA controllerbased internal DMA controller

2.4 Video EngineVideo Engine

• Video decodingVideo decoding

– H.265 MP@L5.0 up to 4K@30fps or 1080p@60fpsH.265 MP@L5.0 up to 4K@30fps or 1080p@60fps

– H.264 BP/MP/HP@L5.0 up to 4K@24fps or 1080p@60fpsH.264 BP/MP/HP@L5.0 up to 4K@24fps or 1080p@60fps

– H.263 BP up to 1080p@60fpsH.263 BP up to 1080p@60fps

– MPEGMPEG-4 SP/ASP L54 SP/ASP L5 up to 1080p@60fpsup to 1080p@60fps

– MPEGMPEG-2 MP/HL up to 1080p@60fps2 MP/HL up to 1080p@60fps

– MPEGMPEG-1 MP/HL up to 1080p@60fps1 MP/HL up to 1080p@60fps

– Xvid up to 1080p@60fpsXvid up to 1080p@60fps

– Sorenson SparkSorenson Spark up to 1080p@60fpsup to 1080p@60fps

– WMV9/VCMV9/VC-1 SP/MP/AP up to 1080p@60fps1 SP/MP/AP up to 1080p@60fps

– MJPEG up to 1080p@30fpsMJPEG up to 1080p@30fps

• Video encodingVideo encoding

– JPEG/MJPEG up to 1080p@60fpsJPEG/MJPEG up to 1080p@60fps

– Supports inputSupports input picture scaler up/downpicture scaler up/down

2.5 Video and GraphicsVideo and Graphics

2.5.1 Display Engine (DE)Display Engine (DE)

• Output size up to 2048 x 2048Output size up to 2048 x 2048 Draft Version

• SupportSupports two alpha blending channels for main displaytwo alpha blending channels for main display and one channel for aux displayand one channel for aux display

• SupportSupports four overlay layers in each channel, and has an independent scalerfour overlay layers in each channel, and has an independent scaler

• SupportSupports potterpotter-duff compatible blending operationduff compatible blending operation

• SupportSupports LBC buffer decoderLBC buffer decoder

• SupportSupports dither output to TCONither output to TCON

• SupportSupports input format input format Semi -planar YUV422/YUV420/YUV411YUV422/YUV420/YUV411 and Planar and Planar YUV422/YUV420/YUV411YUV422/YUV420/YUV411, ARGB8888/XRGB8888/RGB888/ARGB4444/ARGB1555ARGB8888/XRGB8888/RGB888/ARGB4444/ARGB1555/RGB565/paletteRGB565/palette

• SupportSupports SmartColorSmartColor2.0 for excellent display experience.0 for excellent display experience

– Adaptive detail/edge enhancementAdaptive detail/edge enhancement

– Adaptive color enhancementAdaptive color enhancement

– Adaptive contrast enhancement and fresh tone rectifyAdaptive contrast enhancement and fresh tone rectify

• SupportSupports write back for aux displaywrite back for aux display

2.5.2 De -interlacer (DI)interlacer (DI)

• Supports YUV420 (Planar/NV12/NVSupports YUV420 (Planar/NV12/NV21) and YUV422 (Planar/NV16/NV61) data format21) and YUV422 (Planar/NV16/NV61) data format

• Support video resolution from 32×32 to 2048×1280 pixelSupport video resolution from 32×32 to 2048×1280 pixel

• Support InterSupport Inter-field interpolation/motion adaptive defield interpolation/motion adaptive de-interlace methodinterlace method

• Performance: module clock 600M for 1080p@60Hz YUV420Performance: module clock 600M for 1080p@60Hz YUV420

2.5.3 Graphic 2D (G2D)Graphic 2D (G2D)

• Supports layerSupports layer size up to 2048 x 2048 pixelssize up to 2048 x 2048 pixels

• Supports preSupports pre-multiply alpha image datamultiply alpha image data

• Supports color keySupports color key

• Supports two pipes PorterSupports two pipes Porter-Duff alpha blendingDuff alpha blending

• Supports multiple video formats 4:2:0, 4:2:2, 4:1:1 and multiple pixel formats (8/16/24/32 bits graphics Supports multiple video formats 4:2:0, 4:2:2, 4:1:1 and multiple pixel formats (8/16/24/32 bits graphics layer)layer)

• Supports Supports memory scan order optionmemory scan order option

• Supports any format convert functionSupports any format convert function

• Supports 1/16× to 32× resize ratioSupports 1/16× to 32× resize ratio

• Supports 32Supports 32-phase 8phase 8-tap horizontal antitap horizontal anti-alias filter and 32alias filter and 32-phase 4phase 4-tap vertical antitap vertical anti-alias filteralias filter

• Supports window clipSupports window clip

• Supports FillRectangle, BitBlit, StretcSupports FillRectangle, BitBlit, StretchBlit and MaskBlithBlit and MaskBlit

• Supports horizontal and vertical flip, clockwise 0/90/180/270 degree rotate for normal bufferSupports horizontal and vertical flip, clockwise 0/90/180/270 degree rotate for normal buffer

• Supports horizontal flip, clockwise 0/90/270 degree rotate for LBC bufferSupports horizontal flip, clockwise 0/90/270 degree rotate for LBC buffer Draft Version

2.6 Video OutputVideo Output

2.6.1 RGB and LVDS LCDRGB and LVDS LCD

• SupportSupports RGB interface with DE/SYNC moRGB interface with DE/SYNC mode, up to 1920de, up to 1920 x 1080@60fps1080@60fps

• SupportSupports serial RGB/dummy RGB interface, up to 800serial RGB/dummy RGB interface, up to 800 x 480@60fps480@60fps

• SupportSupports LVDS interface with dual link, up to 1920LVDS interface with dual link, up to 1920 x 1080@60fps1080@60fps

• SupportSupports LVDS interface with single link,LVDS interface with single link, up to 1366up to 1366 x 768@60fps768@60fps

• SupportSupports i8080 interface, up to 800i8080 interface, up to 800 x 480@60fps480@60fps

• SupportSupports BT 656 interface for NTSC and PAL656 interface for NTSC and PAL

• RGB888, RGB666 and RGB565 with dither functionRGB888, RGB666 and RGB565 with dither function

• Gamma correction with R/G/B channel independenceGamma correction with R/G/B channel independence

2.6.2 MIPI DSIMIPI DSI

• Compliance withCompliance with MIPI DSI v1.01MIPI DSI v1.01

• Supports 4Supports 4-lane MIPI DSI, up to lane MIPI DSI, up to 1280 x 720@60fps and 1920 x 1200@1280 x 720@60fps and 1920 x 1200@60fps60fps

• SupportSupports nons non-burstburst mode with sync pulse/sync eventmode with sync pulse/sync event, burst mode and command mode, burst mode and command mode

• SupportSupports pixel format: pixel format: RGB888, RGB666, RGB666 RGB888, RGB666, RGB666 loosely loosely packedpacked and RGB565and RGB565

• Supports continuous and nonSupports continuous and non-continuous lane clock modescontinuous lane clock modes

• SupportSupports bidirectional bidirectional communication of alcommunication of all generic commands in LP through data lane 0l generic commands in LP through data lane 0

• Supports Supports low ow power ower data ata transmissionransmission

• Supports ULPS and Supports ULPS and escape modesescape modes

• Hardware checksum capabilitiesHardware checksum capabilities

2.6.3 HDMIHDMI

• Compatible with HDCompatible with HDMI 2.0MI 2.0

• Supports DDC and SCDCSupports DDC and SCDC

• Integrated CEC hardware engineIntegrated CEC hardware engine

• OptioOptional color space convertnal color space converter (CSC)er (CSC): RGB (4:4:4) to/from YCbCr (4:4:4 or 4:2:2)RGB (4:4:4) to/from YCbCr (4:4:4 or 4:2:2)

• Video Video formatsformats:

– All CEAAll CEA-861861-E video formats up to 1080p at 60 Hz and 720p/1080i at 120 HzE video formats up to 1080p at 60 Hz and 720p/1080i at 120 Hz

– Optional HDMI 1.4b video formatsOptional HDMI 1.4b video formats

All CEAAll CEA-861861-E video formats up to 1080p at 120 HzE video formats up to 1080p at 120 Hz

HDMI 1.4b 4K x 2K video formatsHDMI 1.4b 4K x 2K video formats Draft Version

HDMI 1.4b 3D video modes with up to 340 MHz (TMDS clock)HDMI 1.4b 3D video modes with up to 340 MHz (TMDS clock)

– Optional HDMI 2.0 video formatsOptional HDMI 2.0 video formats

All CEAAll CEA-861861-F video formatsF video formats

Dynamic Range and Mastering InfoFrame (DRM, packet header 0x87)Dynamic Range and Mastering InfoFrame (DRM, packet header 0x87)

• Audio Audio formatsformats:

– Uncompressed audio formats: IEC60985 L-PCM audio samples, up to 192 kHz

– Compressed audio formats: IEC61937 compressed audio, up to 1536 kHz (for HDMI 2.0b)/768 kHz (for HDMI 1.4b)

2.6.4 CVBS OUTCVBS OUT

• 1-channel CVBchannel CVBS outputoutput

• Supports Supports NTSC and PAL formatNTSC and PAL format

• Plug status auto detectingPlug status auto detecting

• 10 bits DAC output

2.7 Video InputVideo Input

2.7.1 Parallel CSIParallel CSI

• Su pports 8pports 8-bit digital camera interface (RAW8/YUV422/YUV420)bit digital camera interface (RAW8/YUV422/YUV420)

• Supports BT656, BT601 interface (YUV422)Supports BT656, BT601 interface (YUV422)

• Supports ITUSupports ITU-R BT.656 timeR BT.656 time-multiplexed format up to 2*1080p@30fps in DDR sample modemultiplexed format up to 2*1080p@30fps in DDR sample mode

• Maximum pixel clock of 148.5 MHzMaximum pixel clock of 148.5 MHz

• Supports deSupports de-interlacing for interlace interlacing for interlace video inputvideo input

• Supports conversion from YUV422 to YUV420, YUV422 to YUV400, YUV420 to YUV400Supports conversion from YUV422 to YUV420, YUV422 to YUV400, YUV420 to YUV400

• Supports horizontal and vertical flipSupports horizontal and vertical flip

2.7.2 CVBS INCVBS IN

• 2-channel CVBS input and 1channel CVBS input and 1-channel CVBS decoderchannel CVBS decoder

• Supportupports NTSC and PAL formatNTSC and PAL format

• Supports YUV422/YUV420 format Supports YUV422/YUV420 format

• With 1 chanWith 1 channel 3D comb filternel 3D comb filter

• Detection for signal locked and 625 linesDetection for signal locked and 625 lines

• Programmable brightness, contrast, and saturationProgrammable brightness, contrast, and saturation

• 10 -bit video ADCsbit video ADCs

2.8 System PeripheralsSystem Peripherals

2.8.1 TimerTimer

• The timer module implements the timing and counting functions, which includes timer0, timer1, The timer module implements the timing and counting functions, which includes timer0, timer1, watchdowatchdog, and audio video synchronization (AVS) g, and audio video synchronization (AVS)

• The timer0/timer1 is a 32The timer0/timer1 is a 32-bit down counter. The timer0 and timer1 are completely consistentbit down counter. The timer0 and timer1 are completely consistent

• The watchdog is used to transmit a reset signal to reset the entire system when an exception occurs in The watchdog is used to transmit a reset signal to reset the entire system when an exception occurs in the systemthe system

• The AVS The AVS is used to synchronize the audio and video. The AVS subis used to synchronize the audio and video. The AVS sub-block includes AVS0 and AVS1, which block includes AVS0 and AVS1, which are completely consistentare completely consistent

2.8.2 High Speed Timer (HSTimer)High Speed Timer (HSTimer)

• The HSTimer module consists of HSTimer0 and HSTimer1. HSTimer0 and HSTimer1 are down counters The HSTimer module consists of HSTimer0 and HSTimer1. HSTimer0 and HSTimer1 are down counters that implement tthat implement timing and counting functions. They are completely consistent.iming and counting functions. They are completely consistent.

• Configurable 56Configurable 56-bit down timerbit down timer

• Supports 5 prescale factorsSupports 5 prescale factors

• The clock source is synchronized with AHBThe clock source is synchronized with AHB0 clock, much more accurate than other timersclock, much more accurate than other timers

• Supports 2 working modes: periodic mode and singSupports 2 working modes: periodic mode and single counting modele counting mode

• Generates an interrupt when the count is decreased to 0Generates an interrupt when the count is decreased to 0

2.8.3 PlatformPlatform-Level Interrupt Controller (PLIC)Level Interrupt Controller (PLIC)

• Samplingampling, priority arbitration and priority arbitration and distribution for external interrupt sourcesdistribution for external interrupt sources

• The interrupt can be configured as machine mode and super usThe interrupt can be configured as machine mode and super user modeer mode

• Up to 256 interrupt source sampling, supporting level interrupt and pulse interruptUp to 256 interrupt source sampling, supporting level interrupt and pulse interrupt

• 32 levels of interrupt priority32 levels of interrupt priority

• Maintains independently the interrupt enable for each interrupt mode (machine/super user)Maintains independently the interrupt enable for each interrupt mode (machine/super user)

• Maintains independently the interrupt threMaintains independently the interrupt threshold shold for each interrupt mode (machine/super user)for each interrupt mode (machine/super user)

• Configurable access permission for PLIC registersConfigurable access permission for PLIC registers

2.8.4 DMACDMAC

• Up to 16Up to 16-ch DMAch DMA

• Provides 32 peripheral DMA requests for data reading and 32 peripheral DMA requests for data writingProvides 32 peripheral DMA requests for data reading and 32 peripheral DMA requests for data writing

• Flexible data width of 8/16/32Flexible data width of 8/16/32/64/64-bit

• Programmable DMA burst lengthProgrammable DMA burst length

• Supports linear and IO address modesSupports linear and IO address modes Draft Version

• Supports data transfer types with memorySupports data transfer types with memory-to -memory, memorymemory, memory-to -peripheral, peripheralperipheral, peripheral-to -memory, memory, peripheralperipheral-to -peripheralperipheral

• Supports transferring data with a linked listSupports transferring data with a linked list

• DRQ response iDRQ response includes waiting mode and handshake modencludes waiting mode and handshake mode

• DMA channel supports pause functionDMA channel supports pause function

• Memory devices support nonMemory devices support non-aligned transformaligned transform

2.8.5 Clock Controller Unit (CCU)Clock Controller Unit (CCU)

• 8 PLLs8 PLLs

• One onOne on-chip RC oscillator chip RC oscillator

• Supports one external 24 MHz DCXO and one external 32.768 kHz oscillatorSupports one external 24 MHz DCXO and one external 32.768 kHz oscillator

• Supports clock configuration and clock generation for corresponding modules Supports clock configuration and clock generation for corresponding modules

• Supports softwareSupports software-controlled clock gating and softwarecontrolled clock gating and software-controlled reset for corresponding modules controlled reset for corresponding modules

2.8.6 Thermal Sensor Controller (THS)Thermal Sensor Controller (THS)

• One thermal sensor located in CPUOne thermal sensor located in CPU

• TemperatureTemperature accuracy: ±3°C from 0°C to +100°C, ±5°C from accuracy: ±3°C from 0°C to +100°C, ±5°C from -25°C to +125°C25°C to +125°C

• Averaging filter for thermal sensor readingAveraging filter for thermal sensor reading

• Supports overSupports over-temperature protection interrupt and overtemperature protection interrupt and over-temperature alarm interrupttemperature alarm interrupt

2.8.7 LDO PowerLDO Power

• Integrated 2 LDOs (LDOA, LDOB) Integrated 2 LDOs (LDOA, LDOB)

• LDOA: 1.8 V power outpuLDOA: 1.8 V power output, LDOB: 1.35 V/1.5 V/1.8 V power output t, LDOB: 1.35 V/1.5 V/1.8 V power output

• LDOA for IO and analog module, LDOB for SDRAMLDOA for IO and analog module, LDOB for SDRAM

• Input voltage is 2.4 V to 3.6 VInput voltage is 2.4 V to 3.6 V

2.8.8 RTCRTC

• Implements time counter and timing wakeupImplements time counter and timing wakeup

• Provides a 16Provides a 16-bit counter for counting day, 5bit counter for counting day, 5-bit counter for counting hour, 6bit counter for counting hour, 6-bit countebit counter for counting r for counting minute, 6minute, 6-bit counter for counting secondbit counter for counting second

• External connect a 32.768 kHz lowExternal connect a 32.768 kHz low-frequency oscillator for count clockfrequency oscillator for count clock

• Timer frequency is 1 kHzTimer frequency is 1 kHz

• Configurable initial value by software anytimeConfigurable initial value by software anytime Draft Version

• Supports timing alarm, and generates interrupt and wakeuSupports timing alarm, and generates interrupt and wakeup the external devicesp the external devices

• 8 general purpose registers for storing power8 general purpose registers for storing power-off informationoff information

2.8.9 ResetReset

• Integrated internal resetIntegrated internal reset

• Reset Reset D1 or other ICor other IC

2.9 Audio SubsystemAudio Subsystem

2.9.1 Audio CodecAudio Codec

• Two audio digitalTwo audio digital-to -analog (DAC) channelsanalog (DAC) channels

– Supports 16Supports 16-bit and 20bit and 20-bit sample resolutionbit sample resolution

– 8 kHz to 192 kHz DAC sample rate8 kHz to 192 kHz DAC sample rate

– 100 ± 2100 ± 2 dB SNRdB SNR@A -weight, weight, -85 ± 3 dB THD+N85 ± 3 dB THD+N

• Two audio outputs:Two audio outputs:

– OneOne stereo headphone output: stereo headphone output: HPOUTL/RHPOUTL/R

– One stereo differential lineout outputOne stereo differential lineout output: LINEOUTLP/N and LINEOUTRP/NLINEOUTLP/N and LINEOUTRP/N

• Three audio analogThree audio analog-to -digital (ADC) channelsdigital (ADC) channels

– Supports 16Supports 16-bit and 20bit and 20-bit sample resolutionbit sample resolution

– 8 kHz to 48 kHz ADC sample rate8 kHz to 48 kHz ADC sample rate

– 95 ± 3dB SNR@A95 ± 3dB SNR@A-weight, weight, -80 ± 3dB THD+N80 ± 3dB THD+N

• Five audio inputs:Five audio inputs:

– ThreeThree differential microphone inputdifferential microphone inputs: MICIN1P/1N, MICIN2P/2N, MICIN3P/3N MICIN1P/1N, MICIN2P/2N, MICIN3P/3N

– One One stereo stereo LINEINLINEIN input : LINEINL/RLINEINL/R

– One One stereo FMstereo FMIN input : FMINL/RFMINL/R

• Stereo headphone driverStereo headphone driver

– 95 ± 3 dB SNR@A95 ± 3 dB SNR@A-weightweight

– Output Level 0.55 Vrms@10 kΩ/THD+N Output Level 0.55 Vrms@10 kΩ/THD+N -77 ± 3 dB77 ± 3 dB, 0.370.37 Vrms@16 Ω/THD+N Vrms@16 Ω/THD+N -40 dB40 dB

• Supports Dynamic Range Controller adjusting the DAC playback and ADC recordingSupports Dynamic Range Controller adjusting the DAC playback and ADC recording

• One 128x20One 128×20-bits FIFO for DAC data transmit, one 128x20bits FIFO for DAC data transmit, one 128×20-bits FIFO for ADC data receivebits FIFO for ADC data receive

• Programmable FIFProgrammable FIFO thresholdsO thresholds

• Supports interrupts and DMASupports interrupts and DMA

• XuanTie C906 RISC-V CPU

• 32 KB I32 KB I-cache + 32 KB Dcache + 32 KB D-cachecache

2.2 DSP ArchitectureDSP Architecture

• HiFi4HiFi4

• 32 KB L1 I32 KB L1 I-cache and 32 KB L1 Dcache and 32 KB L1 D-cache cache

• 64 KB I64 KB I-ram and 64 KB Dram and 64 KB D-ramram

2.3 Memory SubsystemMemory Subsystem

2.3.1 Boot ROM (BROM) Boot ROM (BROM)

• On -chip memorychip memory

• Supports system boot from the following devices:Supports system boot from the following devices:

– SD cardSD card

– eMMCeMMC

– SPI SPI NOR FlashNOR Flash

– SPI NAND FlashSPI NAND Flash

• Supports mandatory upgrade process through USBSupports mandatory upgrade process through USB and SD cardand SD card

• Supports GPIO pin Supports GPIO pin and eFuse module and eFuse module to select the boot media typeto select the boot media type

2.3.2 SDRAMSDRAM

• Supports DDR2/DDR3 SDRAMSupports DDR2/DDR3 SDRAM

• Maximum capacity up to 2 GBaximum capacity up to 2 GB

• Supports clock frequSupports clock frequency up to 533 MHz for DDR2ency up to 533 MHz for DDR2

• Supports clock frequency up to 800 MHz for DDR3Supports clock frequency up to 800 MHz for DDR3

2.3.3 SMHC SMHC

• Three SD/MMC host controller (SMHC) interfacesThree SD/MMC host controller (SMHC) interfaces

• The SMHC0 controls the devices that comply with the protocol Secure Digital Memory (SD memThe SMHC0 controls the devices that comply with the protocol Secure Digital Memory (SD mem-version version 3.0)3.0) Draft Version

• The SMHC1 controls the device that complies with The SMHC1 controls the device that complies with the protocol Secure Digital I/O (SDIOthe protocol Secure Digital I/O (SDIO-version 3.0)version 3.0)

• The SMHC2 controls the device that complies with the protocol Multimedia Card (eMMCThe SMHC2 controls the device that complies with the protocol Multimedia Card (eMMC-version 5.0)version 5.0)

• Maximum performance:Maximum performance:

– SDR mode 1SDR mode 150 MHz@1.8 V50 MHz@1.8 V IO pad IO pad

– DDR mode DDR mode 100 MHz@1.8 V100 MHz@1.8 V IO padIO pad

– DDR mode 50 MHz@3.3 V IO padDDR mode 50 MHz@3.3 V IO pad

• Supports 1Supports 1-bit or 4bit or 4-bit data widthbit data width

• Supports block size of 1 to 65535 bytesSupports block size of 1 to 65535 bytes

• Internal 1024Internal 1024-Bytes RX FIFO and 1024Bytes RX FIFO and 1024-Bytes TX FIFOBytes TX FIFO

• Supports cSupports card insertion and removal ard insertion and removal interruptinterrupt

• Supports hardSupports hardware CRC generation and error detectionware CRC generation and error detection

• Supports descriptorSupports descriptor-based internal DMA controllerbased internal DMA controller

2.4 Video EngineVideo Engine

• Video decodingVideo decoding

– H.265 MP@L5.0 up to 4K@30fps or 1080p@60fpsH.265 MP@L5.0 up to 4K@30fps or 1080p@60fps

– H.264 BP/MP/HP@L5.0 up to 4K@24fps or 1080p@60fpsH.264 BP/MP/HP@L5.0 up to 4K@24fps or 1080p@60fps

– H.263 BP up to 1080p@60fpsH.263 BP up to 1080p@60fps

– MPEGMPEG-4 SP/ASP L54 SP/ASP L5 up to 1080p@60fpsup to 1080p@60fps

– MPEGMPEG-2 MP/HL up to 1080p@60fps2 MP/HL up to 1080p@60fps

– MPEGMPEG-1 MP/HL up to 1080p@60fps1 MP/HL up to 1080p@60fps

– Xvid up to 1080p@60fpsXvid up to 1080p@60fps

– Sorenson SparkSorenson Spark up to 1080p@60fpsup to 1080p@60fps

– WMV9/VCMV9/VC-1 SP/MP/AP up to 1080p@60fps1 SP/MP/AP up to 1080p@60fps

– MJPEG up to 1080p@30fpsMJPEG up to 1080p@30fps

• Video encodingVideo encoding

– JPEG/MJPEG up to 1080p@60fpsJPEG/MJPEG up to 1080p@60fps

– Supports inputSupports input picture scaler up/downpicture scaler up/down

2.5 Video and GraphicsVideo and Graphics

2.5.1 Display Engine (DE)Display Engine (DE)

• Output size up to 2048 x 2048Output size up to 2048 x 2048 Draft Version

• SupportSupports two alpha blending channels for main displaytwo alpha blending channels for main display and one channel for aux displayand one channel for aux display

• SupportSupports four overlay layers in each channel, and has an independent scalerfour overlay layers in each channel, and has an independent scaler

• SupportSupports potterpotter-duff compatible blending operationduff compatible blending operation

• SupportSupports LBC buffer decoderLBC buffer decoder

• SupportSupports dither output to TCONither output to TCON

• SupportSupports input format input format Semi -planar YUV422/YUV420/YUV411YUV422/YUV420/YUV411 and Planar and Planar YUV422/YUV420/YUV411YUV422/YUV420/YUV411, ARGB8888/XRGB8888/RGB888/ARGB4444/ARGB1555ARGB8888/XRGB8888/RGB888/ARGB4444/ARGB1555/RGB565/paletteRGB565/palette

• SupportSupports SmartColorSmartColor2.0 for excellent display experience.0 for excellent display experience

– Adaptive detail/edge enhancementAdaptive detail/edge enhancement

– Adaptive color enhancementAdaptive color enhancement

– Adaptive contrast enhancement and fresh tone rectifyAdaptive contrast enhancement and fresh tone rectify

• SupportSupports write back for aux displaywrite back for aux display

2.5.2 De -interlacer (DI)interlacer (DI)

• Supports YUV420 (Planar/NV12/NVSupports YUV420 (Planar/NV12/NV21) and YUV422 (Planar/NV16/NV61) data format21) and YUV422 (Planar/NV16/NV61) data format

• Support video resolution from 32×32 to 2048×1280 pixelSupport video resolution from 32×32 to 2048×1280 pixel

• Support InterSupport Inter-field interpolation/motion adaptive defield interpolation/motion adaptive de-interlace methodinterlace method

• Performance: module clock 600M for 1080p@60Hz YUV420Performance: module clock 600M for 1080p@60Hz YUV420

2.5.3 Graphic 2D (G2D)Graphic 2D (G2D)

• Supports layerSupports layer size up to 2048 x 2048 pixelssize up to 2048 x 2048 pixels

• Supports preSupports pre-multiply alpha image datamultiply alpha image data

• Supports color keySupports color key

• Supports two pipes PorterSupports two pipes Porter-Duff alpha blendingDuff alpha blending

• Supports multiple video formats 4:2:0, 4:2:2, 4:1:1 and multiple pixel formats (8/16/24/32 bits graphics Supports multiple video formats 4:2:0, 4:2:2, 4:1:1 and multiple pixel formats (8/16/24/32 bits graphics layer)layer)

• Supports Supports memory scan order optionmemory scan order option

• Supports any format convert functionSupports any format convert function

• Supports 1/16× to 32× resize ratioSupports 1/16× to 32× resize ratio

• Supports 32Supports 32-phase 8phase 8-tap horizontal antitap horizontal anti-alias filter and 32alias filter and 32-phase 4phase 4-tap vertical antitap vertical anti-alias filteralias filter

• Supports window clipSupports window clip

• Supports FillRectangle, BitBlit, StretcSupports FillRectangle, BitBlit, StretchBlit and MaskBlithBlit and MaskBlit

• Supports horizontal and vertical flip, clockwise 0/90/180/270 degree rotate for normal bufferSupports horizontal and vertical flip, clockwise 0/90/180/270 degree rotate for normal buffer

• Supports horizontal flip, clockwise 0/90/270 degree rotate for LBC bufferSupports horizontal flip, clockwise 0/90/270 degree rotate for LBC buffer Draft Version

2.6 Video OutputVideo Output

2.6.1 RGB and LVDS LCDRGB and LVDS LCD

• SupportSupports RGB interface with DE/SYNC moRGB interface with DE/SYNC mode, up to 1920de, up to 1920 x 1080@60fps1080@60fps

• SupportSupports serial RGB/dummy RGB interface, up to 800serial RGB/dummy RGB interface, up to 800 x 480@60fps480@60fps

• SupportSupports LVDS interface with dual link, up to 1920LVDS interface with dual link, up to 1920 x 1080@60fps1080@60fps

• SupportSupports LVDS interface with single link,LVDS interface with single link, up to 1366up to 1366 x 768@60fps768@60fps

• SupportSupports i8080 interface, up to 800i8080 interface, up to 800 x 480@60fps480@60fps

• SupportSupports BT 656 interface for NTSC and PAL656 interface for NTSC and PAL

• RGB888, RGB666 and RGB565 with dither functionRGB888, RGB666 and RGB565 with dither function

• Gamma correction with R/G/B channel independenceGamma correction with R/G/B channel independence

2.6.2 MIPI DSIMIPI DSI

• Compliance withCompliance with MIPI DSI v1.01MIPI DSI v1.01

• Supports 4Supports 4-lane MIPI DSI, up to lane MIPI DSI, up to 1280 x 720@60fps and 1920 x 1200@1280 x 720@60fps and 1920 x 1200@60fps60fps

• SupportSupports nons non-burstburst mode with sync pulse/sync eventmode with sync pulse/sync event, burst mode and command mode, burst mode and command mode

• SupportSupports pixel format: pixel format: RGB888, RGB666, RGB666 RGB888, RGB666, RGB666 loosely loosely packedpacked and RGB565and RGB565

• Supports continuous and nonSupports continuous and non-continuous lane clock modescontinuous lane clock modes

• SupportSupports bidirectional bidirectional communication of alcommunication of all generic commands in LP through data lane 0l generic commands in LP through data lane 0

• Supports Supports low ow power ower data ata transmissionransmission

• Supports ULPS and Supports ULPS and escape modesescape modes

• Hardware checksum capabilitiesHardware checksum capabilities

2.6.3 HDMIHDMI

• Compatible with HDCompatible with HDMI 2.0MI 2.0

• Supports DDC and SCDCSupports DDC and SCDC

• Integrated CEC hardware engineIntegrated CEC hardware engine

• OptioOptional color space convertnal color space converter (CSC)er (CSC): RGB (4:4:4) to/from YCbCr (4:4:4 or 4:2:2)RGB (4:4:4) to/from YCbCr (4:4:4 or 4:2:2)

• Video Video formatsformats:

– All CEAAll CEA-861861-E video formats up to 1080p at 60 Hz and 720p/1080i at 120 HzE video formats up to 1080p at 60 Hz and 720p/1080i at 120 Hz

– Optional HDMI 1.4b video formatsOptional HDMI 1.4b video formats

All CEAAll CEA-861861-E video formats up to 1080p at 120 HzE video formats up to 1080p at 120 Hz

HDMI 1.4b 4K x 2K video formatsHDMI 1.4b 4K x 2K video formats Draft Version

HDMI 1.4b 3D video modes with up to 340 MHz (TMDS clock)HDMI 1.4b 3D video modes with up to 340 MHz (TMDS clock)

– Optional HDMI 2.0 video formatsOptional HDMI 2.0 video formats

All CEAAll CEA-861861-F video formatsF video formats

Dynamic Range and Mastering InfoFrame (DRM, packet header 0x87)Dynamic Range and Mastering InfoFrame (DRM, packet header 0x87)

• Audio Audio formatsformats:

– Uncompressed audio formats: IEC60985 L-PCM audio samples, up to 192 kHz

– Compressed audio formats: IEC61937 compressed audio, up to 1536 kHz (for HDMI 2.0b)/768 kHz (for HDMI 1.4b)

2.6.4 CVBS OUTCVBS OUT

• 1-channel CVBchannel CVBS outputoutput

• Supports Supports NTSC and PAL formatNTSC and PAL format

• Plug status auto detectingPlug status auto detecting

• 10 bits DAC output

2.7 Video InputVideo Input

2.7.1 Parallel CSIParallel CSI

• Su pports 8pports 8-bit digital camera interface (RAW8/YUV422/YUV420)bit digital camera interface (RAW8/YUV422/YUV420)

• Supports BT656, BT601 interface (YUV422)Supports BT656, BT601 interface (YUV422)

• Supports ITUSupports ITU-R BT.656 timeR BT.656 time-multiplexed format up to 2*1080p@30fps in DDR sample modemultiplexed format up to 2*1080p@30fps in DDR sample mode

• Maximum pixel clock of 148.5 MHzMaximum pixel clock of 148.5 MHz

• Supports deSupports de-interlacing for interlace interlacing for interlace video inputvideo input

• Supports conversion from YUV422 to YUV420, YUV422 to YUV400, YUV420 to YUV400Supports conversion from YUV422 to YUV420, YUV422 to YUV400, YUV420 to YUV400

• Supports horizontal and vertical flipSupports horizontal and vertical flip

2.7.2 CVBS INCVBS IN

• 2-channel CVBS input and 1channel CVBS input and 1-channel CVBS decoderchannel CVBS decoder

• Supportupports NTSC and PAL formatNTSC and PAL format

• Supports YUV422/YUV420 format Supports YUV422/YUV420 format

• With 1 chanWith 1 channel 3D comb filternel 3D comb filter

• Detection for signal locked and 625 linesDetection for signal locked and 625 lines

• Programmable brightness, contrast, and saturationProgrammable brightness, contrast, and saturation

• 10 -bit video ADCsbit video ADCs

2.8 System PeripheralsSystem Peripherals

2.8.1 TimerTimer

• The timer module implements the timing and counting functions, which includes timer0, timer1, The timer module implements the timing and counting functions, which includes timer0, timer1, watchdowatchdog, and audio video synchronization (AVS) g, and audio video synchronization (AVS)

• The timer0/timer1 is a 32The timer0/timer1 is a 32-bit down counter. The timer0 and timer1 are completely consistentbit down counter. The timer0 and timer1 are completely consistent

• The watchdog is used to transmit a reset signal to reset the entire system when an exception occurs in The watchdog is used to transmit a reset signal to reset the entire system when an exception occurs in the systemthe system

• The AVS The AVS is used to synchronize the audio and video. The AVS subis used to synchronize the audio and video. The AVS sub-block includes AVS0 and AVS1, which block includes AVS0 and AVS1, which are completely consistentare completely consistent

2.8.2 High Speed Timer (HSTimer)High Speed Timer (HSTimer)

• The HSTimer module consists of HSTimer0 and HSTimer1. HSTimer0 and HSTimer1 are down counters The HSTimer module consists of HSTimer0 and HSTimer1. HSTimer0 and HSTimer1 are down counters that implement tthat implement timing and counting functions. They are completely consistent.iming and counting functions. They are completely consistent.

• Configurable 56Configurable 56-bit down timerbit down timer

• Supports 5 prescale factorsSupports 5 prescale factors

• The clock source is synchronized with AHBThe clock source is synchronized with AHB0 clock, much more accurate than other timersclock, much more accurate than other timers

• Supports 2 working modes: periodic mode and singSupports 2 working modes: periodic mode and single counting modele counting mode

• Generates an interrupt when the count is decreased to 0Generates an interrupt when the count is decreased to 0

2.8.3 PlatformPlatform-Level Interrupt Controller (PLIC)Level Interrupt Controller (PLIC)

• Samplingampling, priority arbitration and priority arbitration and distribution for external interrupt sourcesdistribution for external interrupt sources

• The interrupt can be configured as machine mode and super usThe interrupt can be configured as machine mode and super user modeer mode

• Up to 256 interrupt source sampling, supporting level interrupt and pulse interruptUp to 256 interrupt source sampling, supporting level interrupt and pulse interrupt

• 32 levels of interrupt priority32 levels of interrupt priority

• Maintains independently the interrupt enable for each interrupt mode (machine/super user)Maintains independently the interrupt enable for each interrupt mode (machine/super user)

• Maintains independently the interrupt threMaintains independently the interrupt threshold shold for each interrupt mode (machine/super user)for each interrupt mode (machine/super user)

• Configurable access permission for PLIC registersConfigurable access permission for PLIC registers

2.8.4 DMACDMAC

• Up to 16Up to 16-ch DMAch DMA

• Provides 32 peripheral DMA requests for data reading and 32 peripheral DMA requests for data writingProvides 32 peripheral DMA requests for data reading and 32 peripheral DMA requests for data writing

• Flexible data width of 8/16/32Flexible data width of 8/16/32/64/64-bit

• Programmable DMA burst lengthProgrammable DMA burst length

• Supports linear and IO address modesSupports linear and IO address modes Draft Version

• Supports data transfer types with memorySupports data transfer types with memory-to -memory, memorymemory, memory-to -peripheral, peripheralperipheral, peripheral-to -memory, memory, peripheralperipheral-to -peripheralperipheral

• Supports transferring data with a linked listSupports transferring data with a linked list

• DRQ response iDRQ response includes waiting mode and handshake modencludes waiting mode and handshake mode

• DMA channel supports pause functionDMA channel supports pause function

• Memory devices support nonMemory devices support non-aligned transformaligned transform

2.8.5 Clock Controller Unit (CCU)Clock Controller Unit (CCU)

• 8 PLLs8 PLLs

• One onOne on-chip RC oscillator chip RC oscillator

• Supports one external 24 MHz DCXO and one external 32.768 kHz oscillatorSupports one external 24 MHz DCXO and one external 32.768 kHz oscillator

• Supports clock configuration and clock generation for corresponding modules Supports clock configuration and clock generation for corresponding modules

• Supports softwareSupports software-controlled clock gating and softwarecontrolled clock gating and software-controlled reset for corresponding modules controlled reset for corresponding modules

2.8.6 Thermal Sensor Controller (THS)Thermal Sensor Controller (THS)

• One thermal sensor located in CPUOne thermal sensor located in CPU

• TemperatureTemperature accuracy: ±3°C from 0°C to +100°C, ±5°C from accuracy: ±3°C from 0°C to +100°C, ±5°C from -25°C to +125°C25°C to +125°C

• Averaging filter for thermal sensor readingAveraging filter for thermal sensor reading

• Supports overSupports over-temperature protection interrupt and overtemperature protection interrupt and over-temperature alarm interrupttemperature alarm interrupt

2.8.7 LDO PowerLDO Power

• Integrated 2 LDOs (LDOA, LDOB) Integrated 2 LDOs (LDOA, LDOB)

• LDOA: 1.8 V power outpuLDOA: 1.8 V power output, LDOB: 1.35 V/1.5 V/1.8 V power output t, LDOB: 1.35 V/1.5 V/1.8 V power output

• LDOA for IO and analog module, LDOB for SDRAMLDOA for IO and analog module, LDOB for SDRAM

• Input voltage is 2.4 V to 3.6 VInput voltage is 2.4 V to 3.6 V

2.8.8 RTCRTC

• Implements time counter and timing wakeupImplements time counter and timing wakeup

• Provides a 16Provides a 16-bit counter for counting day, 5bit counter for counting day, 5-bit counter for counting hour, 6bit counter for counting hour, 6-bit countebit counter for counting r for counting minute, 6minute, 6-bit counter for counting secondbit counter for counting second

• External connect a 32.768 kHz lowExternal connect a 32.768 kHz low-frequency oscillator for count clockfrequency oscillator for count clock

• Timer frequency is 1 kHzTimer frequency is 1 kHz

• Configurable initial value by software anytimeConfigurable initial value by software anytime Draft Version

• Supports timing alarm, and generates interrupt and wakeuSupports timing alarm, and generates interrupt and wakeup the external devicesp the external devices

• 8 general purpose registers for storing power8 general purpose registers for storing power-off informationoff information

2.8.9 ResetReset

• Integrated internal resetIntegrated internal reset

• Reset Reset D1 or other ICor other IC

2.9 Audio SubsystemAudio Subsystem

2.9.1 Audio CodecAudio Codec

• Two audio digitalTwo audio digital-to -analog (DAC) channelsanalog (DAC) channels

– Supports 16Supports 16-bit and 20bit and 20-bit sample resolutionbit sample resolution

– 8 kHz to 192 kHz DAC sample rate8 kHz to 192 kHz DAC sample rate

– 100 ± 2100 ± 2 dB SNRdB SNR@A -weight, weight, -85 ± 3 dB THD+N85 ± 3 dB THD+N

• Two audio outputs:Two audio outputs:

– OneOne stereo headphone output: stereo headphone output: HPOUTL/RHPOUTL/R

– One stereo differential lineout outputOne stereo differential lineout output: LINEOUTLP/N and LINEOUTRP/NLINEOUTLP/N and LINEOUTRP/N

• Three audio analogThree audio analog-to -digital (ADC) channelsdigital (ADC) channels

– Supports 16Supports 16-bit and 20bit and 20-bit sample resolutionbit sample resolution

– 8 kHz to 48 kHz ADC sample rate8 kHz to 48 kHz ADC sample rate

– 95 ± 3dB SNR@A95 ± 3dB SNR@A-weight, weight, -80 ± 3dB THD+N80 ± 3dB THD+N

• Five audio inputs:Five audio inputs:

– ThreeThree differential microphone inputdifferential microphone inputs: MICIN1P/1N, MICIN2P/2N, MICIN3P/3N MICIN1P/1N, MICIN2P/2N, MICIN3P/3N

– One One stereo stereo LINEINLINEIN input : LINEINL/RLINEINL/R

– One One stereo FMstereo FMIN input : FMINL/RFMINL/R

• Stereo headphone driverStereo headphone driver

– 95 ± 3 dB SNR@A95 ± 3 dB SNR@A-weightweight

– Output Level 0.55 Vrms@10 kΩ/THD+N Output Level 0.55 Vrms@10 kΩ/THD+N -77 ± 3 dB77 ± 3 dB, 0.370.37 Vrms@16 Ω/THD+N Vrms@16 Ω/THD+N -40 dB40 dB

• Supports Dynamic Range Controller adjusting the DAC playback and ADC recordingSupports Dynamic Range Controller adjusting the DAC playback and ADC recording

• One 128x20One 128×20-bits FIFO for DAC data transmit, one 128x20bits FIFO for DAC data transmit, one 128×20-bits FIFO for ADC data receivebits FIFO for ADC data receive

• Programmable FIFProgrammable FIFO thresholdsO thresholds

• Supports interrupts and DMASupports interrupts and DMA

2.9.2 I2S/PCM

•Three I2S/PCM external interfaces (I2S0, I2S1, I2S2) for connecting external power amplifier and MIC

ADC

•Compliant with standard Philips Inter

-IC sound (I2S) bus specification

-Left-justified, Right-justified, PCM mode, and Time Division Multiplexing (TDM)format

-Programmable

PCM frame width: 1 BCLK width (short frame) and 2 BCLKs width (long frame)

•Transmit and Receive data FIFOs

-Programmable FIFO thresholds

-128 depth x 32-bit width TXFIFO and 64 depth x 32-bit width RXFIFO

•Supports multiple function clock

-Clock up to 24.576 MHz Data Output of I2S/PCM in Master mode (Only if the IO PAD and Peripheral I2S/PCM satisfy T iming Parameters)

-Clock up to 12.288 MHz Data Input of I2S/PCM in Master mode

•Supports TX/RX DMA slave interface

•Supports multiple application scenarios

-Up to 16 channels (fs = 48 kHz) which has adjustable width from 8

-bit to 32-bit

-Sample rate from 8 kHz to 384 kHz (CHAN = 2)

-8-bit u-law and 8-bit A-law companded sample

•Supports master/slave mode

2.9.3 DMIC

•Supports maximum 8 digital PDM microphones

•Supports sample rate from 8 kHz to 48 kHz

2.9.4 One Wire Audio (OWA)

•One OWA TX

•Compliance with S/PDIF interface

•IEC-60958 transmitter functionality

•Supports 16-bit, 20-bit, and 24-bit data formats

•One 128×24bits TXFIFO for audio data transfer

•Programmable FIFO thresholds

•Supports TX DMA slave interface

•Function clock includes 24.576 MHz and 22.579 MHz frequency

•Hardware parity generation on the transmitter

•Supports channel status insertion for the transmitter

•Supports interrupts and DMA

2.10 Security System

2.10.1 Crypto Engine (CE)

•Supports Symmetrical algorithm for encryption and decryption: AES, DES, TDES

-Supports ECB, CBC, CTS, CTR, CFB, OFB mode for AES

-Supports 128/192/256-bit key for AES

-Supports ECB, CBC, CTR mode for DES/TDES

•Supports Hash algorithm for tamper proofing: MD5, SHA, HMAC

-Supports SHA1, SHA224, SHA256, SHA384, SHA512 for SHA

-Supports HMAC

-SHA1, HMAC

-SHA256 for HMAC

-Supports multi-package mode for MD5/SHA1/SHA224/SHA256/SHA384/SHA512

•Supports Asymmetrical algorithm for signature verification: RSA

-RSA supports 512/1024/2048-bit width

•Supports 160-bit hardware PRNG with 175-bit seed

•Supports 256-bit hardware TRNG

•Internal DMA controller for data transfer with memory

2.10.2 Security ID (SID)

•Supports 2 Kbits eFuse

•Backup eFuse information by using SID_SRAM

•Burning the key to the SID

•Reading the key use status in the SID

•Loading the key to the CE

2.10.3 Secure Memory Control (SMC)

•The SMC is always secure, only secure CPU can access the SMC

•Sets secure area of DRAM

•Sets secure property that Master accesses to DRAM

2.10.4Secure Peripherals Control (SPC)

•The SPC is always secure, only secure CPU can access the SPC

•Sets secure property of peripherals

2.11 External Peripherals

2.11.1 USB DRD

•One USB 2.0 DRD (USB0), with integrated USB 2.0 analog PHY

•Complies with USB2.0 Specification

•Supports USB Host function-Compatible with Enhanced Host Controller Interface (EHCI) Specification, Version 1.0

-Compatible with Open Host Controller Interface (OHCI) Specification, Version 1.0a

-Supports High-Speed (HS, 480 Mbit/s), Full-Speed (FS, 12 Mbit/s), and Low-Speed (LS,1.5 Mbit/s)

-Supports only 1 USB Root port shared between EHCI and OHCI

•Supports USB Device function

-Supports High-Speed (HS, 480 Mbit/s) and Full-Speed (FS, 12 Mbit/s)

-Supports bi-directional endpoint0 (EP0) for Control transfer

-Up to 10 user-configurable endpoints (EP1+, EP1-, EP2+, EP2-, EP3+, EP3-, EP4+, EP4-, EP5+, EP5-)for Bulk transfer, Isochronous transfer and Interrupt transfer

-Up to (8 KB + 64 Bytes) FIFO for all EPs (including EP0)

-Supports interface to an external Normal DMA controller for every EP

•Supports an internal DMA controller for data transfer with memory

•Supports High

-Bandwidth Isochronous & Interrupt transfers

•Automated splitting/combining of packets for Bulk transfers

•Supports point-to-point and point-to-multipoint transfer in both Host and Peripheral modes

•Includes automatic ping capabilities

•Soft connect/disconnect function

•Performs all transaction scheduling in hardware

•Power optimization and power management capabilities

•Device and host controller share a 8K SRAM and a physical PHY

2.11.2USB HOST

•One USB 2.0 HOST (USB1), with integrated USB 2.0 analog PHY

•Complies with USB2.0 Specification

•Supports USB2.0 Host function

-Compatible withEnhanced Host Controller Interface (EHCI) Specification, Version 1.0

-Compatible with Open Host Controller Interface (OHCI) Specification, Version 1.0a

-Supports High

-Speed (HS, 480Mbit/s), Full

-Speed (FS, 12 Mbit/s) and Low

-Speed (LS, 1.5 Mbit/s)Device

-Supports only 1 USB Root port shared between EHCI and OHCI

•An internal DMA Controller for data transfer with memory

2.11.3 EMAC

•One EMAC interface for connecting external Ethernet PHY

•10/100/1000 Mbit/s Ethernet port with RGMII and RMII interfaces

•Compliant with IEEE 802.3-2002 standard

•Supports both full

-duplex and half

-duplex operations

•Provides the management data input/output (MDIO) interface for PHY device configuration and management with configurable clock frequencies

•Programmable frame length to support Standard or Jumbo Ethernet frames with sizes up to 16 KB

•Supports a variety of flexible address filtering modes

•Separate 32

-bit status returned for transmission and reception packets

•Optimization for packet

-oriented DMA transfers with frame delimiters

-Supports linked

-list descriptor list structure

-Descriptor architecture, allowing large blocks of data transfer with minimum CPU intervention; each descriptor can transfer up to 4 KB of data

-Comprehensive status reporting for normal operation and transfers with errors

•4 KB TXFIFO for transmission packets and 16 KB RXFIFO for reception packets

•Programmable interrupt options for different operational conditions

2.11.4 UART

•Up to6UART controllers (UART0, UART1, UART2, UART3,

UART4, UART5)

•UART0, UART4, UART5: 2-wire; UART1, UART2, UART3: 4-wire

•Compatible with industry-standard 16450/16550 UARTs

•Supports IrDA-compatible slow infrared (SIR) format

•Two separate FIFOs: one is RX FIFO, and the other is TX FIFO

-Each of them is 64 bytes (For UART0)

-Each of them is 256 bytes (For UART1, UART2, UART3, UART4, and UART5)

•The working reference clock is from the APB bus clock

-Speed up to 4 Mbit/s with 64 MHz APB clock

-Speed up to 1.5 Mbit/s with 24 MHz APB clock

•5 to 8 data bits for RS

-232 characters, or 9 bits RS-485 format

•1, 1.5 or 2 stop bits

•Programmable parity (even, odd, or no parity)

•Supports TX/RX DMA slave controller interface

•Supports software/hardware flow control

•Supports RX DMA Master interface (Only for UART1)

•Supports auto-flow by using CTS & RTS (Only for UART1/2/3)

2.11.5 SPI and SPI_DBI

•Up to 2 SPI controllers (SPI0, SPI1)

•The SPI0 only supports SPI mode; The SPI1 supports SPI mode and display bus interface (DBI) mode

•SPI mode:

-Full-duplex synchronous serial interface

-Master/slave configurable

-Mode0 to Mode3 are supported for both transmit and receive operations

-8-bit wide by 64

-entry FIFO for both transmit and receive data

-Polarity and phase of the Chip Select (SPI

-CS) and SPI Clock (SPI

-CLK) are configurable

-Supports 3-wire/4

-wire SPI

-Supports programmable serial data frame length: 1-bit to 32-bit

-Supports Standard SPI, Dual

-Output/Dual

-Input SPI, Dual IO SPI, Quad

-Output/Quad

-Input SPI

•DBI mode:

-Supports DBI Type C 3 Line/4 Line Interface Mode

-Supports 2 Data Lane Interface Mode

-Supports RGB111/444/565/666/888 video format

-Maximum resolution of RGB666 240 x 320@30Hz with single data lane

-Maximum resolution of RGB888 240 x 320@60Hz or 320 x 480@30Hz with dual data lane

-Supports Tearing effect

-Supports software flexible control video frame rate

2.11.6 Two Wire Interface (TWI)

•Up to 4 TWI controllers (TWI0, TWI1,TWI2, TWI3)

•Compliant with I2C bus standard

•Supports standard mode (up to 100 kbit/s) and fast mode (up to 400 kbit/s)

•Supports 7

-bit and 10

-bit device addressing modes

•Supports master mode or slave mode

•Master mode features:

-Supports the bus arbitration in the case of multiple master devices

-Supports clock synchronization and bit and byte waiting

-Supports packet transmission and DMA

•Slave mode features:

-Interrupt on address detection

•The TWI controller includes one TWI engine and one TWI driver. And the TWI driver supports packet transmission and DMA mode when TWI works in master mode

2.11.7 CIR Receiver (CIR_RX)

•One CIR_RX interface (IR-RX)

•Full physical layer implementation

•Supports NEC format infra data

•Supports CIR for remote control or wireless keyboard

•64×8 bits FIFO for data buffer

•Sample clock up to 1 MHz

2.11.8 CIR Transmitter (CIR_TX)

•One CIR_TX interface (IR-TX)

•Supports arbitrary wave generator

•Configurable carrier frequency

•Supports handshake mode and waiting mode of DMA

•128 bytes FIFO for data buffer

2.11.9 PWM

•Supports 8 independent PWM channels (PWM0 to PWM7)

-Supports

PWM continuous mode output

-Supports PWM pulse mode output, and the pulse number is configurable

-Output frequency range: 0 to 24 MHz or 100 MHz

-Various duty

-cycle: 0% to 100%

-Minimum resolution: 1/65536

•Supports 4 complementary pairs output

-PWM01 pair (PWM0 + PWM1), PWM23 pair (PWM2 + PWM3), PWM45 pair (PWM4 + PWM5),PWM67 pair (PWM6 + PWM7)

-Supports dead-zone generator, and the dead

-zone time is configurable

•Supports 4 group of PWM channel output for controlling stepping motors

-Supports any plural channels to form a group, and output the same duty

-cycle pulse-In group mode, the relative phase of the output waveform for each channel is configurable

•Supports 8 channels capture input

-Supports rising edge detection and falling edge detection for input waveform pulse

-Supports pulse-width measurement for input waveform pulse

2.11.10 General Purpose ADC (GPADC)

•2-ch successive approximation register (SAR) analog-to-digital converter (ADC)

•12-bit sampling resolution and 8-bit precision

•64 FIFO depth of data register

•Power reference voltage: AVCC, analog input voltage range: 0 to AVCC

•Maximum sampling frequency up to 1 MHz

•Supports three operation modes: single conversion mode, continuous conversion mode, burst conversion mode

2.11.11 Touch Panel ADC(TPADC)

•12 bit SAR type A/D converter

•Configurable sample frequency up to 1 MHz

•One 32×12 FIFO for storing A/D conversion result

•Supports DMA slave interface

•Supports 4-wire resistive touch panel input detection

-Supports pen down detection with programmable sensitivity

-Supports single touch coordinate measurement

-Supports dual touch detection

-Supports touch pressure measurement with programmable threshold

-Supports median and averaging filter for noise reduction

-Supports X and Y coordinate exchange function

•Supports Aux ADC with up to 4 channels

2.11.12 Low Rate ADC(LRADC)

•One LRADC input channel

•6-bit sampling resolution and 5-bit precision

•Sample rate up to 2 kHz

•Supports hold Key and general Key

•Supports normal, continuous and single working mode

•Power supply voltage: AVCC, power reference

voltage: 0.75*AVCC, analog input and detected voltage

range: 0 to 1.266 V

2.11.13 LEDC

•LEDC is used to control the external intelligent control LED lamp

•Configurable LED output high/low level width

•Configurable LED reset time

•LEDC data supports DMA configuration mode and CPU configuration mode

•Maximum 1024 LEDs serial connect

•LED data transfer rate up to 800 kbit/s

2.12 Package

•LFBGA 337 balls,13 mm x 13 mm body size,0.65 mm ball pitch, 0.35 mm ball size

点击查看更多芯片的datasheet。