全志T5芯片是一款高性能四核Cortex-A53平台,是专门面向汽车市场的新一代SoC,通过汽车AEC-Q100测试。全志T5集成Cortex-A53四核CPU、G31 MP2 GPU,支持32位DDR3/LPDDR3/DDR4/LPDDR4 DRAM,拥有多视频输出接口(RGB/2*LVDS/HDMI/CVBS-OUT),多视频输入接口(MIPI CSI/BT656/BT1120)。T5芯片支持4K@60fps H.265解码,4K@25fps H.264编码。支持DI、3D降噪、SmartColor系统和keystone校正模块,提供流畅的用户体验和专业的视觉效果。T5芯片主要应用于机器视觉和高清显示类产品。

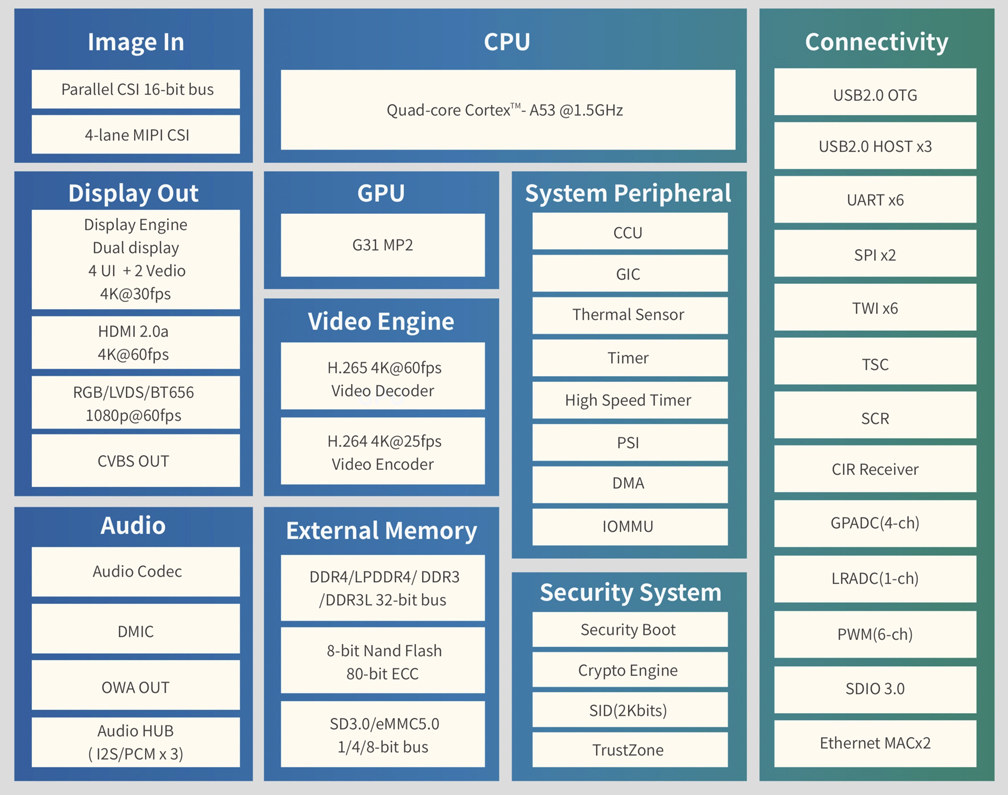

Allwinner T5 specifications:

Allwinner T5 specifications:

- CPU – Quad-core Arm Cortex-A53@1.5GHz

- GPU – Arm Mali G31 MP2 with support for OpenGL ES 3.2/2.0/1.0, Vulkan 1.1, OpenCL 2.0

- Memory I/F – 32-bit DDR4/DDR3/DDR3L/LPDDR3/LPDDR4 interface up to 4GB

- Storage I/F

- SD3.0/eMMC5.0 interface

- 8-bit Nand flash interface with maximum 80-bit/1KB ECC

- Video Engine

- Video decoder

- H.265 MP decoder up to 4K @ 60fps

- H.264 BL/MP/HP decoder up to 4K @ 30fps

- VP9 decoder up to 4K @ 60fps

- AVS2 decoder up to 4K @ 60fps

- Multi-format 1080p60 video playback including VP8, MPEG1/2 SP/MP, MPEG4 SP/ASP, AVS+/AVS JIZHUN, VC1 SP/MP

- Video encoder -H.264 encoder up to 4K @ 25fps, MJPEG encoder up to 4K @ 15fps, JPEG encoder up to 8K x 8K resolution

- Video decoder

- Video Output

- HDMI 2.0a up to 4K @ 60fps

- TV CVBS output (PAL/NTSC)

- Dual-channel LVDS interface up to 1080p @ 60fps

- RGB interface with DE/SYNC mode up to 1080p@60fps

- Video Input

- 1x 8-/10-/12-/16-bit digital camera interface up to 148.5MHz pixel clock

- BT656, BT1120 video input for multichannel YUV

- 4-lane MIPI CSI up to 1Gbps per lane compliant with MIPI-CSI2 V1.00 and MIPI DPHY V1.00

- Maximum video capture resolution of 8M @ 30fps or 4x 1080p @ 25fps for MIPI CSI

- Supported formats – YUV422, YUV420, RAW-8, RAW-10, RAW-12

- Audio

- 2x DAC channels and 4x ADC channels

- 1x audio output interface (differential LINEOUTP/N or single-end LINEOUTL/LINEOUTR)

- Audio HUB with internal mixing function

- 3x I2S/PCM interfaces (I2S0 for extended audio codec, I2S2 for BT, I2S3 for digital power amplifier)

- Supports Left-justified, Right-justified, Standard I2S mode, PCM mode, and TDM mode

- I2S mode supports up to 8 channels and 32-bit/192kbit sample rate

- I2S and TDM modes support a maximum of 16 channels and 32-bit/96kbit sample rate

- 1x 16-/20-/24-bit OWA (One Wire Audio) IOUT interface

- Support for up to 8x digital PDM microphones

- Ethernet – 2x Ethernet MAC (one 10/100 Mbps Ethernet port with RMII interface, one 10/100/1000 Mbps Ethernet port with RGMII and RMII interfaces)

- USB – 3x USB2.0 Host, 1x USB2.0 OTG

- Other Peripherals

- SDIO 3.0, TSC, SCR, CIR Receiver

- 6x TWI, 2x SPI, 6x UART

- 6-ch PWM, 4-ch GPADC, 1-ch LRADC

- Security Engine

- Full Disk Encryption

- AES, DES, 3DES, and XTS encryption algorithms

- MD5, SHA, and HMAC hash

- RSA, ECC signature and verification algorithms

- 160-bit hardware pseudo-random number generator (PRNG) with 175-bit seed

- 256-bit hardware true random number generator (TRNG)

- 2K-bit EFUSE for chip ID and security application

- PMIC – Companion Allwinner Power Management IC

- Package – TFBGA 421 balls; 15 mm x 15 mm size,0.65 mm ball pitch,0.35 mm ball size

- Process – 28nm HPC

- Temperature Range – -40 to 85℃

- Automotive AEC-Q100 qualification