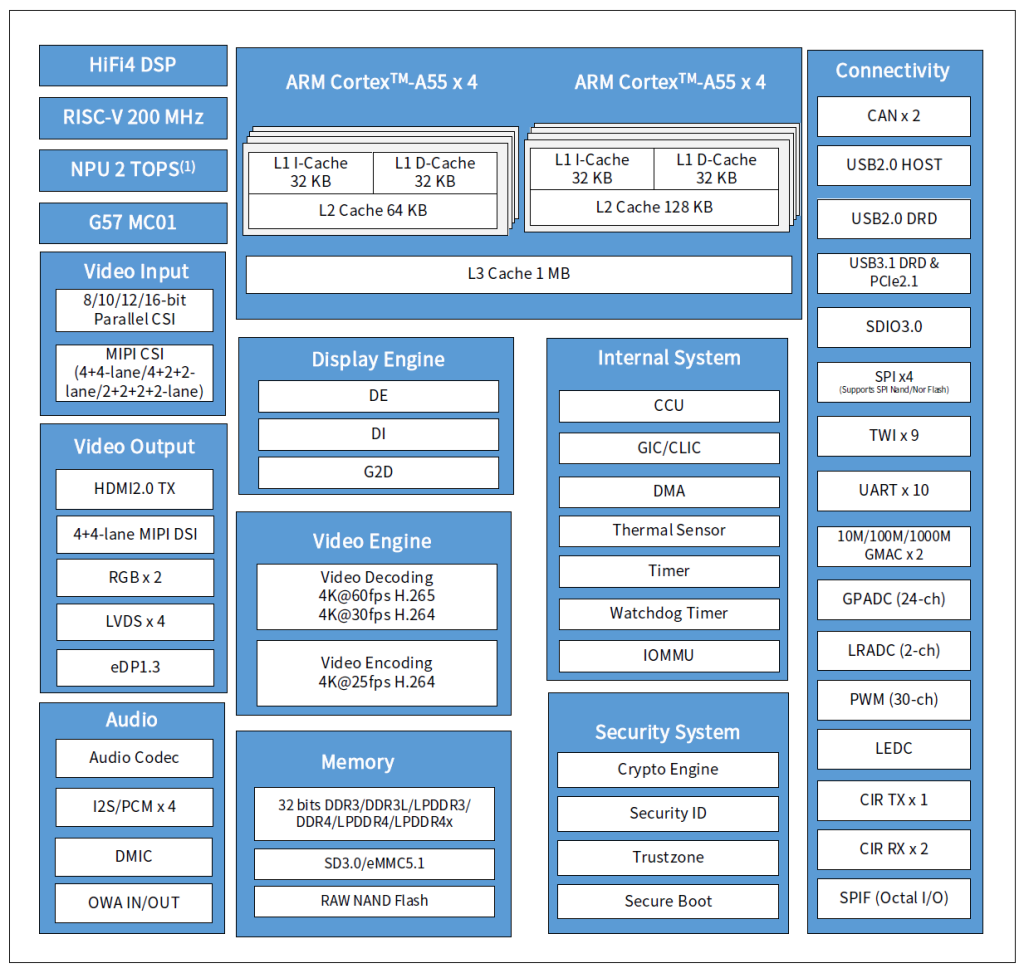

全志T527系列SoC是面向商用电子、工业和汽车领域,具有高性能八核Cortex™-A55 AI平台。集成了八核Cortex-A55 CPU、RISC-V MCU核心、HiFi4 DSP、2 TOPS NPU、G57 MC1 GPU、高速接口(PCIe2.1和USB3.1)、汽车接口(CAN)、多种视频输出接口和视频输入接口。支持4K@60fps H.265解码器、4K@30fps H.264解码器、4K@25fps H.264编码器、DI和AWonder系统,为用户提供了流畅的体验和专业的AI视觉效果。T527系列可用于内容共享和自助交互终端、智能制造以及其他电子商业和工业设备。

特性

- CPU架构

- 八核ARM Cortex™-A55,采用DynamIQ big.LITTLE配置,最高频率1.8 GHz。

- 每个A55核心具有32 KB L1 I-cache和32 KB L1 D-cache。

- 可选64KB L2缓存每个“LITTLE”核心。

- 可选128KB L2缓存每个“big”核心。

- RISC-V CPU,最高频率200 MHz。

- 16 KB I-cache和16 KB D-cache。

- 支持RV32IMAFC指令。

- NPU架构

- 2 TOPS NPU。

- 嵌入式512KB内部缓冲区。

- 支持深度学习框架:TensorFlow、Caffe、TFLite、Pytorch、Onnx NN等。

- GPU架构

- ARM G57 MC1 GPU。

- 支持OpenGL ES 3.2/2.0/1.1、Vulkan1.1/1.2/1.3和OpenCL2.2。

- 支持反锯齿算法。

- 在3D图形处理中具有高内存带宽和低功耗。

- DSP架构

- HiFi4音频DSP。

- 32 KB I-cache + 32 KB D-cache。

- 内存子系统

- 启动ROM(BROM)。

- 片上内存。

- 支持从以下设备启动系统:

- SD卡

- eMMC

- RAW NAND Flash

- SPI NOR Flash(四模式和单模式)

- SPI NAND Flash

- 支持通过USB或SD卡进行强制升级过程。

- 支持GPADC0引脚和eFuse模块选择启动介质类型。

- 支持正常启动和安全启动。

- 安全BROM仅加载认证固件。

- 安全BROM确保安全启动是一个可信环境。

- RAW NAND Flash

- 每1024字节最多支持80位ECC。

- 支持1K/2K/4K/8K/16K/32K字节页面大小。

- 支持最多8位数据总线宽度。

- 支持SLC/MLC闪存和EF-NAND。

- 支持SDR、ONFI DDR1.0、Toggle DDR1.0、ONFI DDR2.0和Toggle DDR2.0 RAW NAND FLASH。

- SDRAM

- 32位DDR3/DDR3L/DDR4/LPDDR3/LPDDR4/LPDDR4X接口。

- 内存容量高达4GB。

- LPDDR3、LPDDR4和LPDDR4X(特别是64位LPDDR3、LPDDR4和LPDDR4X)有4个芯片选择线。

- DDR3、DDR3L和LPDDR3的时钟频率高达1066 MHz。

- DDR4、LPDDR4和LPDDR4x的时钟频率高达1200 MHz。

- SMHC

- 三个SD/MMC主机控制器(SMHC)接口。

- SMHC0,符合安全数字存储卡(SD3.0)协议。

- SMHC1,符合安全数字I/O(SDIO3.0)协议。

- SMHC2,符合多媒体卡(eMMC5.1)协议。

- SMHC0和SMHC1支持以下内容:

- 1位或4位数据宽度。

- 最大性能:

- SDR模式200 MHz@1.8 V IO垫。

- DDR模式50 MHz@1.8 V IO垫。

- SDR模式50 MHz@3.3 V IO垫。

- SMHC2支持以下内容:

- 1位、4位或8位数据宽度。

- 支持HS400模式和HS200模式。

- 最大性能:

- SDR模式200 MHz@1.8V IO垫。

- DDR模式50 MHz@1.8V IO垫。

- SDR模式50 MHz@3.3V IO垫。

- DDR模式50 MHz@3.3V IO垫。

- 支持1到65535字节的块大小。

- 支持硬件CRC生成和错误检测。

视频和图形

- 显示引擎(DE)

- 最大输出尺寸4096 x 2048。

- 支持主显示和两个显示输出的七个alpha混合通道。

- 每个通道支持四个叠加层,并具有独立的缩放器。

- 支持与potter-duff兼容的混合操作。

- 支持AFBC缓冲区解码器。

- 支持垂直梯形校正。

- 输入格式:

- YUV422/YUV420/YUV411/P010/P210的半平面格式。

- YUV422/YUV420/YUV411的平面格式。

- ARGB8888/XRGB8888/RGB888/ARGB4444/ARGB1555/RGB565。

- 输出格式:8位或10位YUV444/YUV422/YUV420/RGB444。

- 帧打包/上下/并排全/并排半3D格式数据。

- HDR视频的10位处理路径。

- AWonder1.0提供卓越的显示体验。

- 自适应去噪,用于压缩噪声或蚊香噪声的yuv420/422输入。

- 自适应超分辨率缩放器。

- 自适应局部动态对比度增强。

- 自适应细节/边缘增强。

- 自适应颜色增强(蓝色拉伸、绿色拉伸和新鲜色调校正)和肤色保护。

- 色调增益、饱和度增益和值增益控制器。

- 完全可编程的颜色矩阵。

- 动态伽马。

- 支持写回以实现高效的双显示和miracast。

- 支持寄存器配置队列以实现寄存器更新功能。

- 去隔行器(DI)

- 仅支持离线处理模式。

- 视频分辨率从32×32到2048×1280像素。

- 输入数据格式:8位NV12/NV21/YV12和平面YUV422/平面YUV422 UV组合。

- 输出数据格式:

- 8位NV12/NV21/YV12和平面YUV422/平面YUV422 UV组合用于DIT。

- YV12/平面YUV422用于TNR。

- 编织/像素运动自适应去隔行方法。

- 时序噪声降低。

- 带有视频胶片检测的胶片模式检测。

- 性能

- 1080P@60Hz YUV420启用所有功能时模块时钟为120MHz。

- 1080P@60Hz YUV422启用所有功能时模块时钟为150MHz。

- 图形2D(G2D)

- 层大小高达2560×2560像素。

- 输入格式和输出格式包括以下内容:

- YUV422(半平面和平面格式)。

- YUV420(半平面和平面格式)。

- P010、P210、P410和Y8。

- ARGB8888、XRGB8888、RGB888、ARGB4444、ARGB1555、ARGB2101010和RGB565。

- 多种旋转类型。

- 水平翻转和垂直翻转。

- 顺时针方向旋转0、90、180或270度。

- 视频引擎

- 视频解码

- 支持ITU-T H.265 Main/Main10,级别6.1。

- 最大视频分辨率:8192×4320。

- 最大解码速率:3840×2160@60fps。

- 支持VP9 Profile0/Profile2,级别6.1。

- 最大视频分辨率:8192 x 4320。

- 最大解码速率:3840×2160@60fps。

- 支持ITU-T H.264 Base/Main/High Profile@Level 4.2。

- 最大视频分辨率:3840 x 2160。

- 最大解码速率:3840×2160@30fps。

- 视频编码

- H.264 BP/MP/HP编码。

- 支持4K@25fps@8bits。

- 最大分辨率:4096 x 4096(1600万像素)。

- 支持I/P帧类型。

- 支持CBR、VBR和FIXEDQP模式。

- 支持感兴趣区域(ROI)编码,最多八个ROI。

- JPEG基线编码。

- JPEG编码器支持4K@15fps。

- JPEG编码器支持YUV420、YUV422和YUV444格式。

- MJPEG基线编码高达4K@15fps。

- 视频解码

- 视频输出

- eDP1.3

- 支持高达2.5K@60fps和4K@30fps。

- 支持1-lane、2-lane或4-lane传输,每lane高达2.7 Gbit/s。

- 视频格式:RGB、YCbCr4:4:4和YCbCr4:2:2。

- 色深:每个通道8位和10位。

- 支持I2S接口。

- 支持单声道、立体声和7.1环绕声。

- 最大采样率:192 KHz。

- 全链路训练。

- 热插拔检测。

- AUX通道。

- 最大工作频率:1MHz。

- 采用Manchester-II编码。

- 时钟展频。

- 可编程电压摆幅和预加重。

- 嵌入式ESD。

- MIPI DSI

- 符合MIPI DSI V1.02。

- 每lane高达1.2 Gbit/s。

- 支持4-lane MIPI DSI,高达1280 x 720@60fps和1920 x 1200@60fps。

- 支持4+4-lane MIPI DSI,高达2560 x 1600@60fps和4096 x 2160@45fps。

- 支持非突发模式与同步脉冲/同步事件、突发模式和命令模式。

- 像素格式:RGB888、RGB666、RGB666松散打包和RGB565。

- 支持连续和非连续lane时钟模式。

- 通用命令支持通过数据lane 0在LP中的双向通信。

- 支持低功耗数据传输。

- 支持ULPS和逃逸模式。

- 支持硬件校验和。

- eDP1.3

- TCON LCD

- 三个TCON LCD控制器:TONC_LCD0、TCON_LCD1和TCON_LCD2。

- TCON_LCD0支持以下内容:

- 支持RGB接口与DE/SYNC模式,高达1920 x 1080@60fps。

- 支持串行RGB/虚拟RGB接口,高达800 x 480@60fps。

- 支持双链路LVDS接口,高达1920 x 1080@60fps。

- 支持单链路LVDS接口,高达1366 x 768@60fps。

- RGB888、RGB666和RGB565的抖动功能。

- 支持i8080接口,高达800 x 480@60fps。

- 支持NTSC和PAL的BT656接口。

- 支持双链路MIPI DSI接口,高达2560×1600@60fps、3840×2160@45fps和4096×2160@45fps。

- 支持单链路MIPI DSI接口,高达1920×1200@60fps。

- TCON_LCD1支持单链路MIPI DSI接口,高达1920×1200@60fps。

- TCON_LCD2支持以下内容:

- 支持RGB接口与DE/SYNC模式,高达1280×720@60fps。

- 支持串行RGB/虚拟RGB接口,高达800×480@60fps。

- 支持i8080接口,高达800×480@60fps。

- 支持NTSC和PAL的BT656接口。

- 支持RGB888、RGB666和RGB565的抖动功能。

- 支持双链路LVDS接口,高达1920×1080@60fps。

- 支持单链路LVDS接口,高达1366×768@60fps。

- TCON TV

- 两个TCON TV控制器:TCON_TV0用于HDMI 2.0b,TCON_TV1用于eDP1.3。

- 支持高达4K@60Hz。

- 输出格式:

- 8位或10位像素深度。

- HV。

- HDMI。

- 一个HDMI2.0 TX接口,支持HDCP1.4。

- 支持2D显示高达4K@60fps和3D显示高达4K@30fps。

- 支持多种数据格式,包括RGB888、YUV444、YUV422和YUV420。

- 支持I2S,192KHz采样率,8个声音通道。

- 支持高达3840×2160@60 10bit输入,3个数据lane,每个lane 6 Gbit/s用于YUV422。

- 支持DDC/CEC,5V耐压。

- 支持3840×2160、1920×1080和1280×720分辨率。

- 视频输入

- ISP

- 支持一个独立的图像信号处理器(ISP),在线模式下最大分辨率为3264×4224。

- 最大帧率为8M@30fps 2F-WDR。

- 支持离线模式。

- 支持WDR split、2F-WDR line-based stitch、动态范围压缩(DRC)、色调映射、数字增益、伽马校正、缺陷像素校正(DPC)、串扰校正(CTC)和色差校正(CAC)。

- 支持2D/3D噪声降低、拜耳插值、锐化、白平衡和颜色增强。

- 可调3A功能:自动白平衡(AWB)、自动曝光(AE)和自动对焦(AF)。

- 支持防闪烁检测统计和直方图统计。

- VIPP

- 四个VIPP YUV422或YUV420输出。

- 最大分辨率为3264×4224。

- 每个VIPP在线模式下有一个子VIPP。

- 每个VIPP在离线模式下最多有四个子VIPP用于时分复用。

- 每个子VIPP支持以下内容:

- 裁剪。

- 高度和宽度的1到1/16缩放。

- 16个ORLs。

- 支持图形镜像和翻转。

- ISP

- MIPI CSI

- 8M@30fps RAW12 2F-WDR,尺寸高达3264(H) x 2448(V)。

- 4+4-lane、4+2+2-lane或2+2+2+2-lane MIPI接口。

- MIPI CSI2 V1.1。

- MIPI DPHY V1.1。

- 每lane 2.0 Gbit/s。

- 裁剪功能。

- 通过软件降低帧率。

- 6个DMA控制器用于6个视频流存储。

- 将隔行输入转换为逐行输出(不支持抗锯齿和噪声降低)。

- 数据转换支持:YUV422到YUV420、YUV422到YUV400、YUV420到YUV400。

- 水平和垂直翻转。

- 并行CSI

- 16位数字相机接口。

- 支持8/10/12/16位宽度。

- 支持BT.656、BT.601、BT.1120接口。

- 双数据速率(DDR)采样模式,像素时钟高达148.5MHz。

- 支持ITU-R BT.656高达4*720P@30fps。

- 支持ITU-R BT.1120高达4*1080P@30fps。

- 系统外设

- 时钟控制器单元(CCU)

- 11个PLL。

- 一个片上RC振荡器。

- 支持一个外部24 MHz DCXO和一个外部32.768 kHz振荡器。

- 支持相应模块的时钟配置和时钟生成。

- 支持相应模块的软件控制时钟门控和软件控制复位。

- DMAC

- 两个16-ch DMA。

- 提供53个外设DMA请求用于数据读取和53个外设DMA请求用于数据写入。

- 使用链表传输数据。

- 灵活的数据宽度:8位、16位或32位。

- 可编程DMA突发长度。

- DRQ响应包括等待模式和握手模式。

- 支持内存设备的非对齐转换。

- 支持以下DMA通道:

- 暂停DMA。

- BMODE和I/O速度模式。

- DMA超时。

- I/O内存管理单元(IOMMU)

- 支持硬件实现的虚拟地址到物理地址映射。

- 支持ISP、CSI、VE_MBUS0、VE_MBUS1、G2D、DE和DI并行地址映射。

- 支持ISP、CSI、VE_MBUS0、VE_MBUS1、G2D、DE和DI独立绕过功能。

- 支持ISP、CSI、VE_MBUS0、VE_MBUS1、G2D、DE和DI独立预取。

- 支持ISP、CSI、VE_MBUS0、VE_MBUS1、G2D、DE和DI独立中断处理机制。

- 支持2级TLB(level1 TLB用于特殊使用,level2 TLB用于共享)。

- 支持TLB完全清除和部分禁用。

- 支持TLB缺失时触发PTW行为。

- 支持检查权限。

- 消息框(MSGBOX)

- 支持通过单向通道在两个CPU之间进行通信。每个CPU都有一个MSGBOX,只能在一个通信中读取或写入。

- CPUX_MSGBOX:CPUS/RISC-V/DSP写入;ARM CPU读取。

- CPUS_MSGBOX:ARM CPU/RISC-V/DSP写入;CPUS读取。

- DSP_MSGBOX:ARM CPU/RISC-V/CPUS写入;DSP读取。

- RISCV_MSGBOX:ARM CPU/CPUS/DSP写入;RISC-V读取。

- 两个CPU之间的通道有4个通道,一个通道的FIFO深度为8 x 32位。

- 支持中断。

- 电源复位时钟管理(PRCM)

- 两个PRCM:STBY_PRCM和MCU_PRCM。

- 1个PLL。

- 总线门控、总线复位和模块时钟配置。

- STBY_PRCM的RAM配置控制。

- RTC。

- 提供一个16位计数器用于计日、5位计数器用于计时、6位计数器用于计分、6位计数器用于计秒。

- 外部连接一个32.768 kHz低频振荡器用于计数时钟。

- 计时器频率为1 kHz。

- 可通过软件随时配置初始值。

- 支持内部32K时钟的扇出功能。

- 支持定时报警,并生成中断和唤醒外部设备。

- 在AON域中存储掉电信息的8个通用寄存器。

- 自旋锁。

- 支持32个锁单元。

- 两种锁状态:锁定和解锁。

- 处理器的锁定时间是可预测的(小于200个周期)。

- 热传感器控制器(THS)。

- 两个THS控制器。

- THS0,包括THS0_0。

- THS1,包括THS1_0、THS1_1、THS1_2和THS1_3。

- 热传感器读数的平均滤波器。

- 支持过温保护中断和过温报警中断。

- 计时器。

- 可配置计数时钟:32KHz、24MHz、16MHz或200MHz。

- 可编程56位倒计时器。

- 两种工作模式:周期模式和单次计数模式。

- 当计数减少到0时生成中断。

- 看门狗定时器(WDT)。

- 支持12个初始值。

- 支持生成超时中断。

- 支持生成复位信号。

- 支持看门狗重启。

- 时钟控制器单元(CCU)

音频子系统

- 音频编解码器

- 两个音频数字模拟转换器(DAC)通道。

- 16位和20位采样分辨率。

- 8 kHz到192 kHz DAC采样率。

- 100 ± 2 dB SNR@A-weight,-85 ± 3 dB THD+N。

- 三个音频输出。

- 一个立体声耳机输出:HPOUTL/R。

- 两个差分线路输出:LINEOUTLP/N和LINEOUTRP/N。

- 三个音频模拟数字转换器(ADC)通道。

- 16位和20位采样分辨率。

- 8 kHz到48 kHz ADC采样率。

- 95 ± 3 dB SNR@A-weight,-80 ± 3 dB THD+N。

- 三个差分麦克风输入:MICIN1P/1N、MICIN2P/2N和MICIN3P/3N(用于回声消除)。

- 两个低噪声模拟麦克风偏置输出:MBIAS和HBIAS。

- 支持动态范围控制器调整DAC播放和ADC录音。

- 一个128×20位FIFO用于DAC数据传输,一个128×20位FIFO用于ADC数据接收。

- 可编程FIFO阈值。

- 支持中断和DMA。

- 内部ALDO输出用于AVCC。

- I2S/PCM

- 四个I2S/PCM外部接口(I2S0、I2S1、I2S2和I2S3)用于连接外部功率放大器和MIC ADC。

- 符合标准飞利浦Inter-IC声音(I2S)总线规范。

- 左对齐、右对齐、PCM模式和时分复用(TDM)格式。

- 可编程PCM帧宽度:1 BCLK宽度(短帧)和2 BCLK宽度(长帧)。

- 用于传输和接收数据的FIFO。

- 可编程FIFO阈值。

- 128深度x 32位宽度TXFIFO和64深度x 32位宽度RXFIFO。

- 支持多种功能时钟。

- 主模式下I2S/PCM数据输出时钟高达24.576 MHz(仅当IO PAD和外围I2S/PCM满足时序参数时)。

- 主模式下I2S/PCM数据输入时钟高达12.288 MHz。

- 支持TX/RX DMA从属接口。

- 支持多种应用场景。

- 最多16个通道(fs = 48 kHz),具有从8位到32位的可调宽度。

- 采样率从8 kHz到384 kHz(采样率 * 通道 * 插槽宽度 ≤ 24.576 MHz)。

- 8位u-law和8位A-law压缩样本。

- 支持主/从模式。

DMIC

- 支持最多8个数字PDM麦克风。

- 支持从8 kHz到48 kHz的采样率。

单线音频(OWA)

- 一个OWA TX和一个OWA RX。

- 符合S/PDIF接口。

- IEC-60958和IEC-61937发送器和接收器功能。

- IEC-60958支持数据格式:16位、20位和24位。

- TXFIFO和RXFIFO。

- 一个128×24位TXFIFO和一个64×24位RXFIFO用于音频数据传输。

- 可编程FIFO阈值。

- 支持TX/RX DMA从属接口。

- 多功能时钟。

- OWA TX和OWA RX的独立时钟。

- TX功能的时钟包括24.576 MHz和22.5792 MHz。

- RX功能的时钟包括24.576*8 MHz。

- 支持TX/RX硬件奇偶校验。

- 发送器上的硬件奇偶校验生成。

- 接收器上的硬件奇偶校验检查。

- 支持接收器上的通道状态捕获。

- 支持接收器上的通道采样率捕获。

- 支持接收器上的插入检测。

- 支持发送器上的通道状态插入。

安全系统

- 加密引擎(CE)

- 对称算法:

- AES对称算法。

- 密钥大小:128/192/256位。

- CFB模式包括:CFB1、CFB8、CFB64和CFB128。

- CTR模式包括:CTR16、CTR32、CTR64和CTR128。

- 支持ECB、CBC、CTS、OFB、CBC-MAC和GCM模式。

- DES对称算法。

- CTR模式,包括:CTR16、CTR32和CTR64。

- 支持ECB、CBC和CBC-MAC模式。

- 支持3DES。

- SM4对称算法支持ECB和CBC模式。

- AES对称算法。

- 哈希算法。

- 支持MD5、SHA1、SHA224、SHA256、SHA384、SHA512和SM3。

- 支持HMAC-SHA1、HMAC-SHA256。

- 随机比特生成器算法。

- 支持PRNG,175位种子宽度,输出为5个字的倍数。

- 支持TRNG,硬件后处理与SHA256,输出为8个字的倍数。

- 公钥算法。

- 支持RSA公钥算法:512/1024/2048/3072/4096位宽度。

- 支持ECC公钥算法:160/224/256/384/521位宽度。

- 支持SM2算法。

- 对称算法:

- 安全ID(SID)

- 4 Kbits eFuse。

- 支持eFuse中的安全和非安全世界。

- SID的寄存器配置始终处于非安全世界。

- 使用SID_SRAM备份eFuse信息。

- 一次性编程。

- 通过参数定义选择双位检查。

- 数据加密。

- 读写保护。

- 安全内存控制(SMC)

- SMC始终是安全的,只有安全CPUX可以访问SMC。

- 设置DRAM的安全区域。

- 支持主设备和地址保护。

- 设置主设备访问DRAM的安全属性。

- 设置DRM区域。

- 最多16个区域,主设备可以访问每个区域。

- 安全外设控制(SPC)

- SPC始终是安全的,只有安全CPU可以访问SPC。

- 设置外设的安全属性。

外部外设

- CIR接收器(CIR_RX)

- 两个CIR_RX接口。

- 完整的物理层实现。

- 支持NEC格式红外数据。

- 支持CIR进行遥控。

- 64×8位FIFO用于数据缓冲。

- 样本时钟高达1 MHz。

- CIR发射器(CIR_TX)

- 一个CIR_TX接口。

- 完整的物理层实现。

- 任意波形发生器。

- 可配置的载波频率。

- DMA的握手模式和等待模式。

- 128字节FIFO用于数据缓冲。

- 支持中断和DMA。

- GMAC

- 一个GMAC接口(GMAC0)用于连接外部以太网PHY。

- 10/100/1000 Mbit/s以太网端口,具有RGMII和RMII接口。

- 符合IEEE 802.3-2002标准。

- 支持全双工和半双工操作。

- 可编程帧长度以支持标准或巨型以太网帧,大小高达16 KB。

- 支持多种灵活的地址过滤模式。

- 分别为传输和接收数据包返回32位状态。

- 优化面向数据包的DMA传输,带有帧分隔符。

- 支持链表描述符列表结构。

- 描述符架构,允许在最小CPU干预下传输大块数据;每个描述符可以传输高达2 KB的数据。

- 正常操作和传输错误的全面状态报告。

- 2 KB TXFIFO用于传输数据包,8 KB RXFIFO用于接收数据包。

- 不同操作条件的可编程中断选项。

- 提供管理数据输入/输出(MDIO)接口,用于PHY设备配置和管理,具有可配置的时钟频率。

- GMAC200

- 一个GMAC接口(GMAC1)用于连接外部以太网PHY。

- 符合IEEE 802.3-2015标准。

- 支持10/100/1000 Mbit/s数据传输速率。

- 支持RMII/RGMII PHY接口。

- AMBA4 AXI主接口,具有64位数据传输。

- 支持全双工和半双工操作。

- 全双工流量控制。

- IEEE 1588-2008用于精确网络时钟同步,支持IEEE 1588-2002和IEEE 1588-2008中描述的以太网数据包时间戳。

- 可编程帧长度以支持标准或巨型以太网帧,大小高达16 KB。

- 源地址字段和VLAN插入或替换,双VLAN。

- 传输TCP/IP校验和卸载。

- 支持多种灵活的地址过滤模式(包括哈希过滤功能)。

- 优化面向数据包的DMA传输,带有帧分隔符。

- 支持链表描述符列表结构。

- 描述符架构,允许在最小CPU干预下传输大块数据:每个描述符可以传输高达32 KB的数据。

- 正常操作和传输错误的全面状态报告。

- 支持4KB TXFIFO用于传输数据包和8KB RXFIFO用于接收数据包。

- 支持16个描述符描述符预取缓存用于TXDMA和RX DMA。

- 不同操作条件的可编程中断选项。

- 支持MDIO接口用于PHY设备配置和管理。

- 可配置传输和接收路径的大端和小端模式

- 支持接收和传输数据包的统计。 – 支持分头。

通用目的ADC(GPADC)

- 两个12-ch SAR ADC。

- 数据寄存器的64 FIFO深度。

- 12位采样分辨率和10位精度。

- 电源参考电压:VCC-ADC,模拟输入电压范围:0到1.8V。

- 最大采样频率高达1 MHz。

- 支持三种操作模式:单次转换模式、连续转换模式、突发转换模式。

LEDC

- 可配置的LED输出高/低电平宽度。

- 可配置的LED复位时间。

- LEDC数据支持DMA配置模式和CPU配置模式。

- 最多1024个LED串联连接。

- 可配置数据包和帧数据之间的间隔时间。

- 可配置RGB显示模式。

低速率ADC(LRADC)

- 2-ch LRADC输入。

- 6位分辨率。

- 采样率高达2 kHz。

- 支持保持键和通用键。

- 支持正常、继续和单次工作模式。

- 电源供应电压:1.8V,电源参考电压:1.35V。

USB2.0 DRD

- 一个USB2.0 DRD(USB0),具有集成的USB 2.0模拟PHY。

- 符合USB2.0规范。

- 支持静态主机操作:

- 与增强型主机控制器接口(EHCI)规范兼容,版本1.0。

- 与开放型主机控制器接口(OHCI)规范兼容,版本1.0a。

- 支持高速(HS,480 Mbit/s)、全速(FS,12 Mbit/s)和低速(LS,1.5 Mbit/s)。

- 仅支持EHCI和OHCI之间共享的1个USB根端口。

- 支持静态设备操作:

- 支持高速(HS,480 Mbit/s)、全速(FS,12 Mbit/s)。

- 支持控制传输的双向端点0(EP0)。

- 支持最多10个用户可配置端点(EP1 IN/OUT、EP2 IN/OUT、EP3 IN/OUT、EP4 IN/OUT、EP5 IN/OUT)用于批量传输、等时传输和中断传输。

- 支持所有EP(包括EP0)的高达(8 KB + 64字节)FIFO。

- 支持每个EP的外部普通DMA控制器接口。

- 支持内存数据传输的内部DMA控制器。

- 支持高带宽等时和中断传输。

- 自动化批量传输的数据包拆分/组合。

- 包括自动PING功能。

- 软连接/断开功能。

- 硬件处理所有数据传输。

- 电源优化和电源管理功能。

- 设备和主机控制器共享一个8K SRAM和一个物理PHY。

USB2.0 HOST

- 一个USB 2.0 HOST(USB1),具有集成的USB 2.0模拟PHY。

- 支持高速(HS,480 Mbit/s)、全速(FS,12 Mbit/s)和低速(LS,1.5 Mbit/s)设备。

- 与增强型主机控制器接口(EHCI)规范兼容,版本1.0。

- 与开放型主机控制器接口(OHCI)规范兼容,版本1.0a。

- 仅支持EHCI和OHCI之间共享的1个USB根端口。

- 一个内部DMA控制器用于内存数据传输。

- 支持UTMI+ Level 3接口和8位双向数据总线。

- 符合行业标准的AMBA高性能总线(AHB),完全符合AMBA规范,修订版2.0。

- 32位小端AMBA AHB从属总线用于寄存器访问。

- 32位小端AMBA AHB主总线用于内存访问。

PCIe2.1&USB3.1系统

- PCIe2.1&USB3.1系统包含1个PCIe2.1&USB3.1组合PHY、1个PCIe2.1控制器和1个USB3.1 DRD控制器。

- PCIe2.1

- 符合PCI Express基础规范,修订版2.1。

- 支持Gen1(2.5 Gbit/s)、Gen2(5.0 Gbit/s)速度。

- 支持Gen1/Gen2的PIPE接口分别以62.5MHz/125 MHz操作。

- Gen1/Gen2模式的恒定32位PIPE宽度。

- 支持根复合体(RC)模式。

- 支持1 lane链路宽度。

- 八个流量类别(TC)。

- 最大有效载荷大小为1K字节。

- 8个入站和8个出站地址转换区域。

- 4个写/读通道用于嵌入式DMA。

- 非发布未决事务的最大数量:32。

- 支持活动状态电源管理(ASPM)。

- 支持高级错误报告(AER)。

- 支持MSI中断。

- USB3.1 DRD

- 注意:

- USB2.0 PHY和USB3.1 PHY共享同一个控制器。它们不能同时使用。

- 一个USB 2.0 UTMI+ PHY(USB2)。

- 一个USB3.1 PIPE PHY(USB3)。

- USB3.1 DRD设备模式支持以下内容:

- USB3.1 PHY的超速(SS,5 Gbit/s)。

- USB2.0 PHY的高速(HS,480 Mbit/s)和全速(FS,12-Mbit/s)。

- USB3.1 DRD主机模式支持以下内容:

- USB3.1 PHY的超速(SS,5 Gbit/s)。

- USB2.0 PHY的高速(HS,480 Mbit/s)、全速(FS,12 Mbit/s)和低速(LS,1.5 Mbit/s)。

- 支持一次设备或主机操作。

- AXI接口用于DMA操作。

- 通过AHB从属接口读取和写入控制和状态寄存器(CSR)。

- 设备模式下最多10个端点,包括控制端点0:

- 5个IN端点:用户EP1 IN、EP2 IN、EP3 IN、EP4 IN、控制EP0 IN。

- 5个OUT端点:用户EP1 OUT、EP2 OUT、EP3 OUT、EP4 OUT、控制EP0 OUT。

- 超速模式下的IN和OUT传输同时进行。

- 双端口接口用于TX数据缓冲、RX数据预取、描述符缓存和寄存器缓存。

- 三个RAM:RX数据FIFO RAM、TX数据FIFO RAM和描述符/寄存器缓存RAM。

- 硬件处理所有数据传输。

- 在多个层面上实现静态和动态电源降低技术。

- 注意:

PWM

- 最多30个PWM通道和4个PWM控制器。

- PWM0-[15:0]用于PWM0控制器。

- PWM1-[3:0]用于PWM1控制器。

- S-PWM0-[1:0]用于S_PWM0控制器。

- MCU-PWM0-[7:0]用于MCU_PWM0控制器。

- PWM控制器最多16个独立PWM通道。

- 支持PWM连续模式输出。

- 支持PWM脉冲模式输出,脉冲数量可配置。

- 输出频率范围:

- 0到24 MHz(时钟源为DCXO24M时)。

- 0到100 MHz(时钟源为APB1时钟时)。

- 各种占空比:0%到100%。

- 最小分辨率:1/65536。

- PWM控制器最多8对互补输出。

- 配对方法如下。组件是PWM输出信号。

- PWM0最多8对:

- PWM0-0 + PWM0-1, PWM0-2 + PWM0-3, PWM0-4 + PWM0-5, PWM0-6 + PWM0-7, PWM0-8 + PWM0-9, PWM0-10 + PWM0-11, PWM0-12 + PWM0-13, PWM0-14 + PWM0-15。

- PWM1最多2对:

- PWM1-0+PWM1-1, PWM1-2+PWM1-3。

- S_PWM0最多1对:S-PWM0-0+ S-PWM0-1。

- MCU_PWM0最多4对:

- MCU-PWM0-0+ MCU-PWM0-1, MCU-PWM0-2+ MCU-PWM0-3, MCU-PWM0-4+ MCU-PWM0-5, MCU-PWM0-6+ MCU-PWM0-7。

- 支持死区发生器,死区时间可配置。

- 最多4组PWM通道输出用于控制步进电机。

- 支持任意多个通道形成一组,并输出相同的占空比脉冲。

- 在组模式下,每个通道的输出波形的相对相位是可配置的。

- 最多16个通道捕获输入。

- 支持输入波形脉冲的上升沿检测和下降沿检测。

- 支持输入波形脉冲的脉宽测量。

- PWM0最多8对:

SPI和SPI_DBI

-

- 最多4个SPI控制器。

- SPI0、SPI2和S_SPI0,支持SPI模式。

- SPI1,支持SPI模式和显示总线接口(DBI)模式SPI模式。

- 多种SPI模式:

- 标准SPI的主模式和从模式。

- 双输出/双输入SPI和双I/O SPI的主模式。

- 四输出/四输入SPI的主模式。

- 3线SPI的主模式,可编程串行数据帧长度为1位到32位。

- 最大时钟频率:100MHz。

- TX/RX DMA从属接口。

- 用于传输和接收数据的8位宽64条目FIFO。

- 支持模式0、模式1、模式2和模式3。

- 芯片选择(SPI_SS)和SPI时钟(SPI_SCLK)的极性和相位是可配置的。

- DBI模式。

- DBI类型C 3线/4线接口模式。

- 2数据通道接口模式。

- RGB111/444/565/666/888视频格式。

- 单数据通道的RGB666最大分辨率为240 x 320@30Hz。

- 双数据通道的RGB888最大分辨率为240 x 320@60Hz或320 x 480@30Hz。

- 撕裂效果。

- 软件灵活控制视频帧率。

- SPI Flash控制器(SPIFC)

- 支持多种SPI模式。

- 标准SPI。

- 双输入/双输出SPI和双I/O SPI。

- 四输入/四输出SPI、四I/O SPI和QPI。

- 八输入/八输出SPI、八I/O SPI和OPI。

- 3线SPI,可编程串行数据帧长度为1位到32位。

- 支持STR模式和DTR模式,DTR模式支持DQS信号。

- 高速时钟频率。

- STR模式为150MHz。

- DTR模式为100MHz。

- 软件写保护。

- 通过软件对所有/部分内存进行写保护。

- 顶部/底部块保护。

- 事务之间的可编程延迟。

- 支持模式0、模式1、模式2和模式3。

- 支持控制信号配置。

- 最多四个芯片选择以支持多个外设。

- 芯片选择(SPI_SS)和SPI时钟(SPI_SCLK)的极性和相位是可配置的。

- 两线接口(TWI)

- 最多9个TWI控制器。

- TWI0、TWI1、TWI2、TWI3、TWI4和TWI5。

- S_TWI0、S_TWI1和S_TWI2。

- 符合I2C总线标准。

- 7位和10位设备寻址模式。

- 标准模式(高达100 Kbit/s)和快速模式(高达400 Kbit/s)。

- 支持通用呼叫和启动字节。

- 主模式支持以下内容:

- 多个主设备情况下的总线仲裁。

- 时钟同步和位及字节等待。

- 数据包传输和DMA。

- 从模式支持地址检测中断。

UART

- 最多10个UART控制器。

- UART0、UART1、UART2、UART3、UART4、UART5、UART6和UART7。

- S_UART0和S_UART1。

- 与行业标准16450/16550 UART兼容。

- 两个独立的FIFO:一个是RX FIFO,另一个是TX FIFO。

- 对于UART0、S_UART0和S_UART1,每个都是64字节。

- 对于UART1、UART2、UART3、UART4、UART5、UART6和UART7,每个都是128字节。

- 工作参考时钟来自APB总线时钟。

- 160 MHz APB时钟时速度高达10 Mbit/s(不包括S_UART0和S_UART1)。

- 80 MHz APB时钟时速度高达5 Mbit/s(不包括S_UART0和S_UART1)。

- 60 MHz APB时钟时速度高达3.75 Mbit/s(不包括S_UART0和S_UART1)。

- 24 MHz APB时钟时速度高达1.5 Mbit/s。

- RS-232格式的5到8位数据位,或RS-485格式的9位数据位。

- 1、1.5或2个停止位。

- 可编程奇偶校验(偶、奇或无)。

- 支持TX/RX DMA从属控制器接口。

- 支持软件/硬件流控制。

- 支持IrDA兼容的慢速红外(SIR)格式。

- 支持使用CTS & RTS的自动流(不包括UART0、S_UART0和S_UART1)。

封装

- HS-FCBGA 664球,尺寸为17 mm x 17 mm,最大高度为1.844 mm,球间距为0.5 mm,球径为0.3 mm。

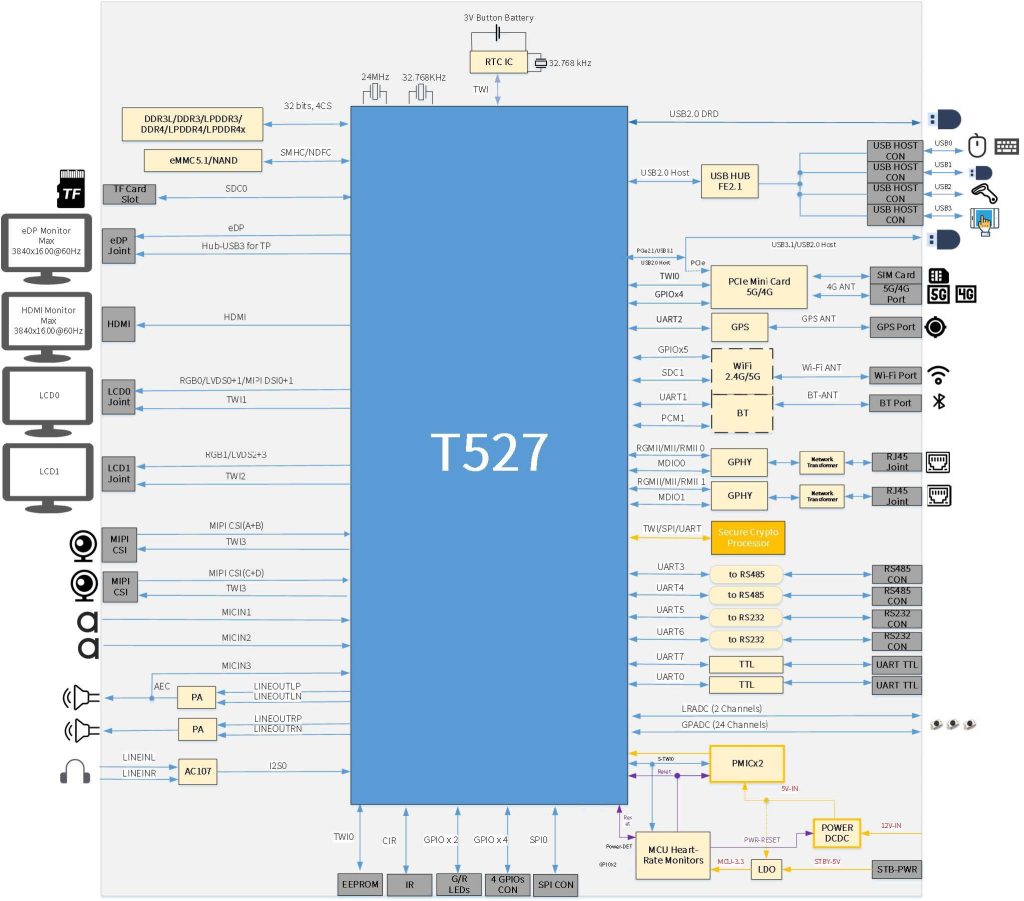

应用示意图