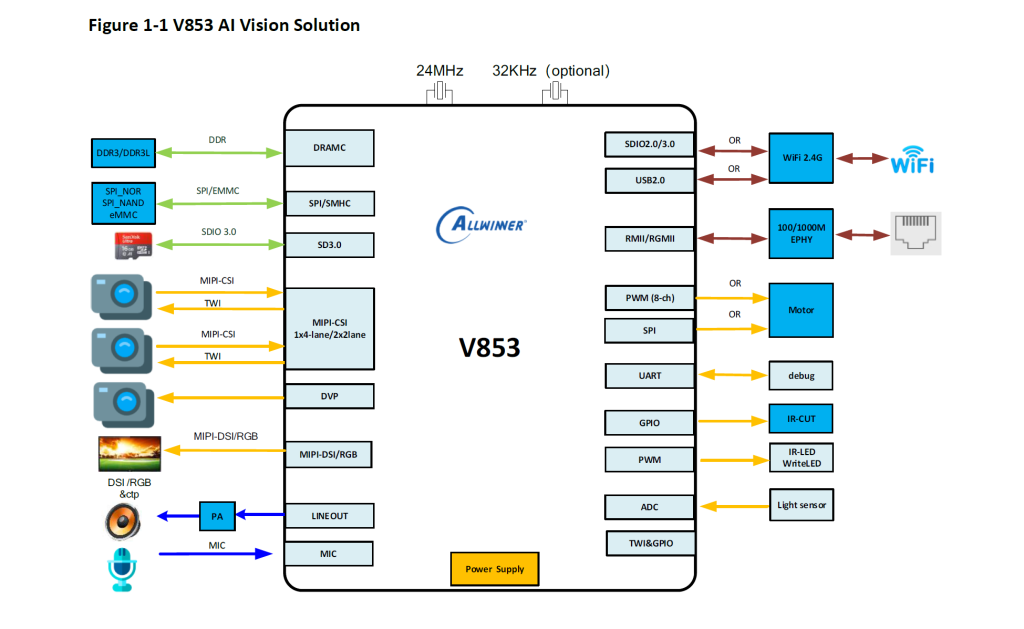

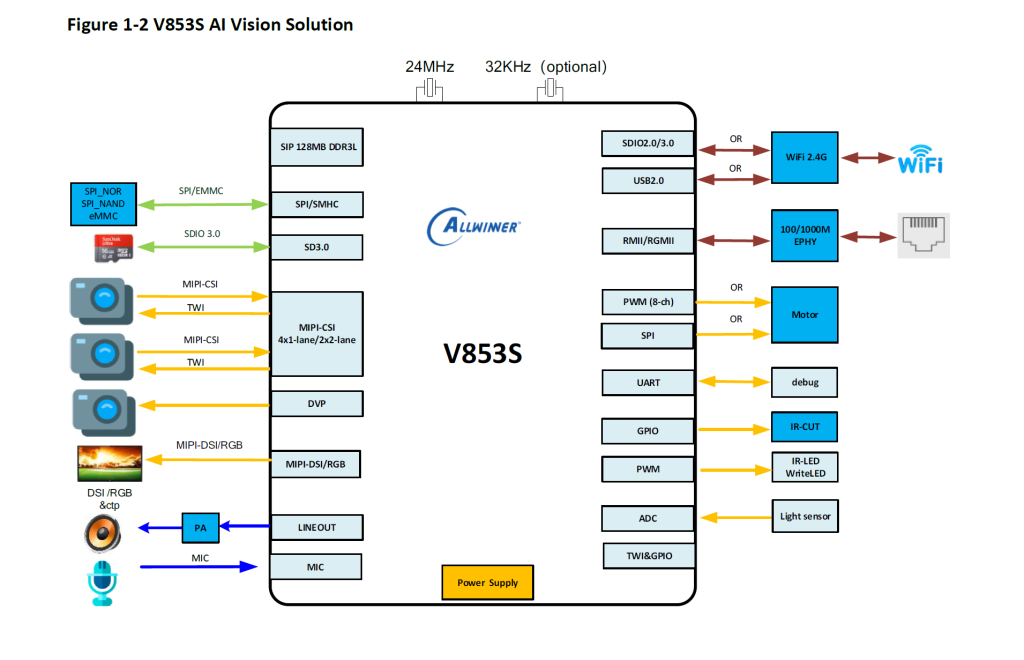

全志V853是一款专门面向机器视觉应用的通用型SoC,采用了ARM Cortex-A7核心和玄铁E907 RISC-V核心的混合架构,集成1 TOPS算力的独立NPU,主要面向低成本的AI Vision应用,如智能门锁、智能门禁、AI网络摄像头、行车记录仪和智能台灯等。SoC采用22nm工艺制造,配备ISP图像处理器和Allwinner Smart视频引擎,最高支持5M@30fps H.265/H。264编码和5M@25fps H.264解码,提供并行CSI和MIPI CSI摄像机接口,以及MIPI DSI和RGB显示接口。

V853是针对智能视觉领域的新一代高性能、低功耗处理器SoC。可广泛应用于智能门锁、智能考勤门禁、网络摄像头、行车记录仪、智能台灯等智能升级行业。V853集成了单个Cortex-A7核心和RISC-V核心。它还设计了新一代高性能ISP图像处理器和Allwinner Smart视频引擎5M@25fpsH.265/H.264编码和5M@25fpsH.264解码,实现专业图片效果。它具有内置NPU,最大1T计算能力,支持INT8/INT16混合操作和典型网络模型,如TensorFlow/MXNet/PyTorch/Caffe。V853采用先进的22nm技术支持产品小型化设计。它还支持1*4通道MIPI/DVP/MIPI-DSI/RGB等各种特殊视频输入输出接口,满足所有AI视频产品的需求。V853支持16位DDR3/DDR3L,以满足各种产品对高带宽的要求。

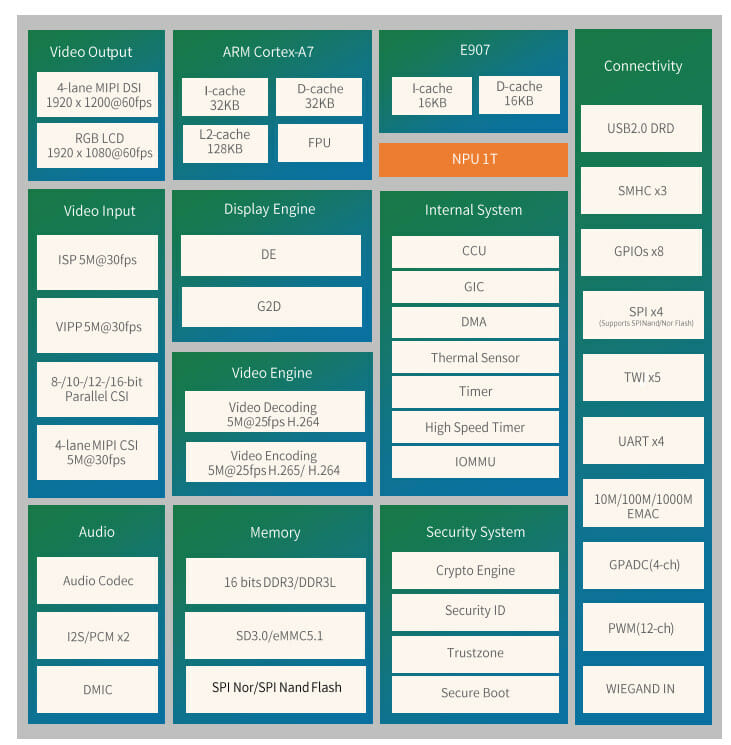

V853 SoC Features

- CPU Architecture

- Cortex-A7 CPU core, supporting 32 KB I-cache, 32 KB D-cache, and 128 KB L2 cache

- RISC-V core, supporting 16 KB I-cache and 16 KB D-cache

- NPU Architecture

- Maximum performance up to 1 Tops for V853 and 0.8 Tops for V853S

- Embedded 128KB internal buffer

- Supports deep learning frameworks: TensorFlow, Caffe, Tflite, Pytorch, Onnx NN, and so on

- Video Encoding/Decoding Performance

- H.264 BP/MP/HP encoding

- H.265 MP encoding

- H.264/H.265 supports I/P frame type

- MJPEG/JPEG baseline encoding

- H.264/JPEG decoding

- Maximum resolution for H.264/H.265 decoding is 16 megapixels (4096×4096)

- A maximum of eight ROIs

- CBR, VBR and FIXEDQP modes

- JPEG encder supports 1080p@60fps@400MHz

- H.264/H.265 encoder supports 3840×2160@20fps@400MHz

- H.264/H.265 multi-stream real-time encoding capability: 5M@25fps + 720p@25fps

- Video Output

- MIPI DSI

- Compliance with MIPI DSI V1.02 and MIPI DPHY V1.2

- Supports 4-lane MIPI DSI, up to 1920 x 1200@60fps

- Supports normal mode and burst mode

- Up to 1.0 Gbps/Lane

- TCONLCD

- i8080 interface, up to 800 x 480@60fps

- Serial RGB interface, up to 800 x 480@60fps

- RGB interface with DE/SYNC mode, up to 1920 x 1080@60fps

- supports BT656 interface

- MIPI DSI

- Video Input

- ISP

- Supports 1 individual image signal processor(ISP), with maximum resolution of 3072 x 3072 (online mode)

- Maximum frame rate of 5M@30fps

- Supports offline mode

- Supports WDR spilt, 2F-WDR line-based stitch, dynamic range compression (DRC), tone mapping, digital gain, gamma correction, defect pixel correction (DPC), cross talk correction (CTC), and chromatic aberration correction (CAC)

- Supports 2D/3D noise reduction, bayer interpolation, sharpen, white balance, and color enhancement

- Adjustable 3A funtions: automatic white balance (AWB), automatic exposure (AE), and automatic focus (AF)

- Supports anti-flick detection statistics, and histogram statistics

- Supports graphics mirror and flip

- VIPP

- Four VIPP YUV422 or YUV420 outputs

- Maximum resolution of 3072×3072

- Each VIPP has one sub-VIPP in online mode

- Each VIPP has maximum four sub-VIPPs for time division multiplexing in offline mode

- Functions for each Sub-VIPP

- Crop

- 1 to 1/16 scaling for height and width

- 16 ORLs

- Parallel CSI

- Supports 8/10/12/16-bit width

- Supports BT.656, BT.601, BT.1120 interface

- Maximum pixel clock for parallel to 148.5MHz

- Supports ITU-R BT.656 up to 4*720P@30fps

- Supports ITU-R BT.1120 up to 4*1080P@30fps

- MIPI CSI

- Supports one 4-lane MIPI CSI input or two 2-lane MIPI CSI inputs

- Compliant with MIPI CSI2 V1.1 and MIPI DPHY V1.1

- Up to 1.2 Gbps/Lane

- maximum video capture resolution for serial interface up to 5M@30fps

- ISP

- Audio Subsystem

- Audio Codec

- One audio digital-to-analog converter (DAC) channels

- Supports 16-bit and 20-bit sample resolution

- 8 kHz to 192 kHz DAC sample rate

- 95 ± 2 dB SNR@A-weight, -85 ± 3 dB THD+N

- Two audio analog-to-digital converter (ADC) channels

- Supports 16-bit and 20-bit sample resolution

- 8 kHz to 48 kHz ADC sample rate

- 95 ± 3dB SNR@A-weight, -80 ± 3dB THD+N

- Two audio inputs:

- Two differential microphone inputs: MICIN1P/N, MICIN2P/N

- One audio output:

- One differential lineout output (LINEOUTP/LINEOUTN)

- Supports Dynamic Range Controller adjusting the DAC playback and ADC recording

- One 128×20-bits FIFO for DAC data transmit, one 128×20-bits FIFO for ADC data receive

- Programmable FIFO thresholds

- Supports interrupts and DMA

- One audio digital-to-analog converter (DAC) channels

- Audio Codec

- I2S

- Two I2S/PCM external interfaces (I2S0, I2S1) for connecting external power amplifier and MIC ADC

- Compliant with standard Philips Inter-IC sound (I2S) bus specification

- Left-justified, Right-justified, PCM mode, and Time Division Multiplexing (TDM) format

- Programmable PCM frame width: 1 BCLK width (short frame) and 2 BCLKs width (long frame)

- Transmit and Receive data FIFOs

- Programmable FIFO thresholds

- 128 depth x 32-bit width TXFIFO and 64 depth x 32-bit width RXFIFO

- Supports multiple function clock

- Clock up to 24.576 MHz Data Output of I2S/PCM in Master mode (Only if the IO PAD and Peripheral I2S/PCM satisfy Timing Parameters)

- Clock up to 12.288 MHz Data Input of I2S/PCM in Master mode

- Supports TX/RX DMA Slave interface

- Supports multiple application scenarios

- Up to 16 channels (fs = 48 kHz) which has adjustable width from 8-bit to 32-bit

- Sample rate from 8 kHz to 384 kHz (CHAN = 2)

- 8-bit u-law and 8-bit A-law companded sample

- Supports master/slave mode

- DMIC

- Supports maximum 8 digital PDM microphones

- Supports sample rate from 8 kHz to 48 kHz

- External Peripherals

- Five TWI interfaces

- Four UART interfaces

- Four SPI interfaces

- Eight GPIO interfaces

- Four channels general purpose analog-to-digital converter(GPADC)

- One PWM controller(12-ch)

点击查看更多芯片的Datasheet。