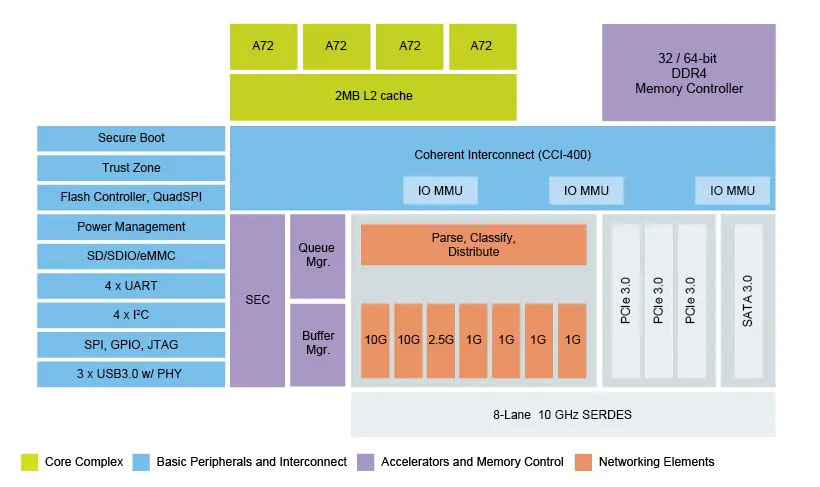

NXP(恩智浦) LS1046A是一款高性能的64位ARM四核处理器。LS1046A处理器将四个64位ARM Cortex-A72内核与数据包处理加速和高速外设相集成。CoreMarks®测试高达45000分,可与10Gb以太网、第三代PCIe、SATA 3.0、USB 3.0和QSPI接口配对,是一系列企业和服务提供商联网、存储、安全和工业应用的完美产品组合。LS1046A可提供稳定的万兆数据通信,在5G领域有出色的性能表现,非常适合5G商用项目定制。

LS1046A处理器特性

- 主频1.2GHz – 1.8GHz ARM Cortex-A72 64位四核

- 48 KB-I和32 KB-D L1缓存

- 2MB L2缓存

- 2x 10 GbE、1x 2.5 GbE和5x GbE

- 八通道SerDes,高达10 GHz,控制器间多路复用,支持:a. 3个第二代PCI Express接口 b. 1个SATA 3.0接口

- DPAA解析、分类和分发引擎

- 内置安全引擎

- 支持DDR4 SDRAM

- 3个PCIe 3.0控制器,x4、x2、x1

- 3个USB 3.0,带有集成式PHY

- SATA 3.0控制器

- 支持Quad SPI接口

- 面向硬件增强虚拟化的Arm SMMU

- 支持可信架构

ScenSmart可为行业客户提供一站式产品解决方案,根据需求定制产品。

LS1046A Features

• LS1046A has four cores and LS1026A has two cores

• Four 32-bit/64-bit Arm® Cortex®-v8 A72 CPUs

– Arranged as a single cluster of four cores sharing asingle 2 MB L2 cache

– Up to 1.8 GHz operation

– Single-threaded cores with 32 KB L1 data cache and48 KB L1 instruction cache

• Hierarchical interconnect fabric

– Up to 700 MHz operation

• One 32-bit/64-bit DDR4 SDRAM memory controllerwith ECC and interleaving support

– Up to 2.1 GT/s

• Data Path Acceleration Architecture (DPAA)incorporating acceleration for the following functions:

– Packet parsing, classification, and distribution(FMan)

– Queue management for scheduling, packetsequencing, and congestion management (QMan)

– Hardware buffer management for buffer allocationand de-allocation (BMan)

– Cryptography acceleration (SEC)

– IEEE 1588™ support

• Two RGMII interfaces

• Eight SerDes lanes for high-speed peripheral interfaces

– Three PCI Express 3.0 controllers

– One Serial ATA (SATA 6 Gbit/s) controller

– Up to two XFI (10 GbE) interfaces

– Up to five SGMII interfaces supporting 1000 Mbps

– Up to three SGMII interfaces supporting 2500 Mbps

– Up to one QSGMII interface

– Supports 10GBase-KR

– Supports 1000Base-KX

• Additional peripheral interfaces

– One Quad Serial Peripheral Interface (QSPI)controller

– One Serial Peripheral Interface (SPI) controller

– Integrated flash controller (IFC) supporting NANDand NOR flash

– Three high-speed USB 3.0 controllers withintegrated PHY

– One Enhanced Secure Digital Host Controllersupporting SD 3.0, eMMC 4.4, and eMMC 4.5

– Four I2C controllers

– Two 16550-compliant DUARTs and six low-powerUARTs (LPUARTs)

– General purpose IO (GPIO), eight Flextimers

– One Queue Direct Memory Access Controller(qDMA)

– One Enhanced Direct Memory Access Controller(eDMA)

– Global programmable interrupt controller (GIC)

– Thermal monitoring unit (TMU)

• 780 FC-PBGA package, 23 mm x 23 mm