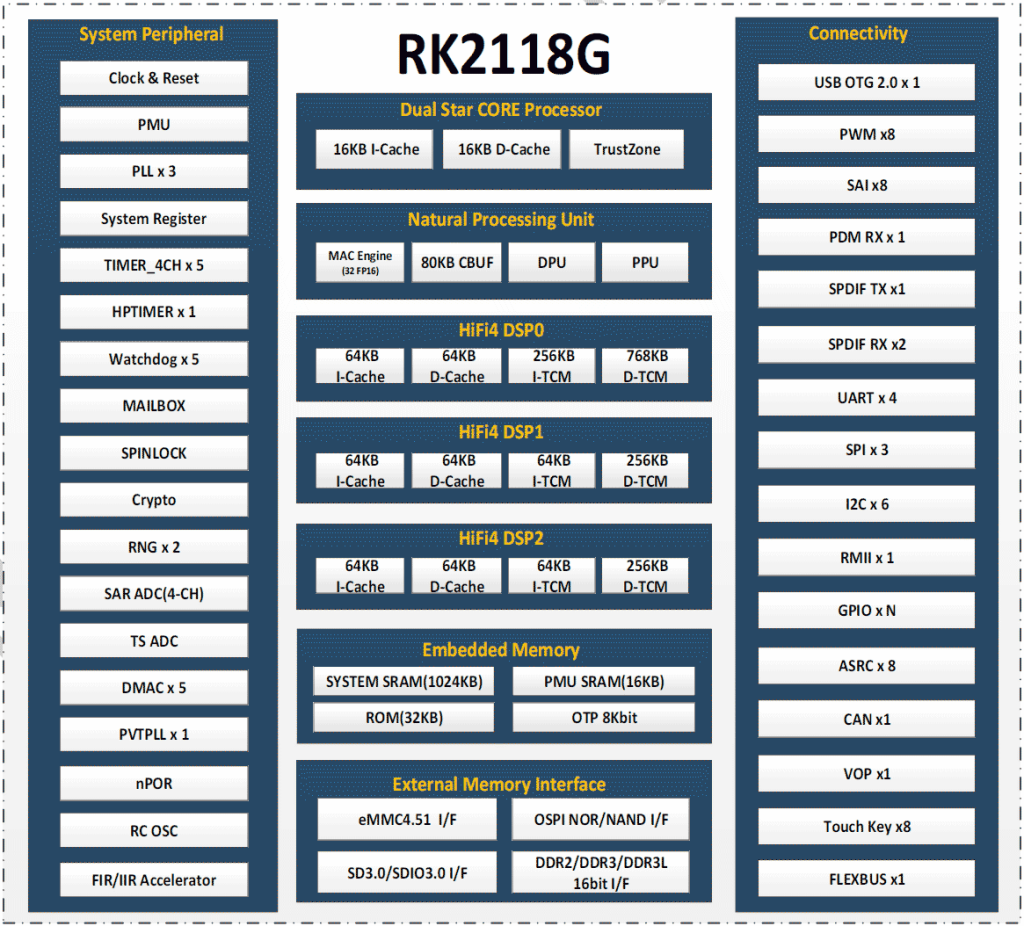

RK2118G是一款高性能三核HiFi4 DSP处理器,专为智能语音交互、音频输入/输出处理和其他数字多媒体应用而设计。嵌入式FIR/IIR加速器和异步采样率转换器硬件引擎,用于最大限度地减少DSP开销,以满足音频处理要求。此外,还集成了一个专门为音频设计的NPU,用于潜在的音频AI处理。

RK2118G集成了双核STAR处理器来运行操作系统、UI渲染和应用程序协议栈等。嵌入式1024KB系统内存和eXecute In-Place(XIP)Flash接口使RK2118G能够灵活地用于不同的应用程序开发。嵌入式外部存储器接口(DDR2/DDR3/DDR3L),能够维持苛刻的存储器带宽。多芯片封装(MCP)可以根据应用需求提供不同容量的片上DDR KGD。

RK2118G集成了双核STAR处理器来运行操作系统、UI渲染和应用程序协议栈等。嵌入式1024KB系统内存和eXecute In-Place(XIP)Flash接口使RK2118G能够灵活地用于不同的应用程序开发。嵌入式外部存储器接口(DDR2/DDR3/DDR3L),能够维持苛刻的存储器带宽。多芯片封装(MCP)可以根据应用需求提供不同容量的片上DDR KGD。

RK2118G集成了丰富的外围接口,如VOP、SAI、PDM、SPDIF、USB2 OTG、RMII、CAN等,可以满足不同应用场景的开发需求,降低硬件开发的复杂性和研发风险,提高整个系统的稳定性。

Microprocessor

- Dual core Star-SE processor, ARM-V8M Architecture

- Support Thumb-2 technology

- Nested Vectored Interrupt Controller (NVIC) closely integrated with the processor

- Support single-precision Floating Point Unit

- Support Enhanced Memory Protection Unit

- Support TrustZone technology

- 16KB I-Cache and 16KB D-Cache

- Serial wire debug port (SW-DP) debug access

DSP

- Three core HiFi4 DSP processor (DSP0, DSP1, DSP2)

- Dual Load/Store, 4 VLIW Slots, 64-bit SIMD

- 4 MAC 32×32, 4 MAC 24×24, 8 MAC 32×16, 8 MAC 16×16 per cycle

- Two 2-Way SIMD VFPU

- 256KB ITCM, 768KB DTCM, 64KB I-Cache, 64KB D-Cache for DSP0

- 64KB ITCM, 256KB DTCM, 64KB I-Cache, 64KB D-Cache for DSP1/DSP2

- One isolated voltage domain for DSP0 DVFS

Neural Process Unit

- Support float point 16bit convolution operation

- 32 float point 16bit MAC operations per cycle

- 80KB internal buffer

- Inference Engine: TensorFlow, Caffe, Tflite, Pytorch, Onnx NN, Android NN,

FIR/IIR Accelerator

- Support simultaneous operation of FIR and IIR

- Support TCB chain structure

- Support legacy mode and max up to 32 TCB

- Support auto configuration mode (ACM), and keep working until TCB pointer is empty

- Support 4096 order FIR filter

- Support Transposed Direct Form II Biquads for IIR, and max 64 biquads cascade

Memory Organization

- Internal on-chip memory

- BootROM

- System SRAM

- PMU SRAM

- External off-chip memory①

- DDR2/DDR3/DDR3L

- SPI Nor/Nand Flash

- eMMC

- SD Card

Internal Memory

- Internal BootRom

- Support system boot from the following device:

- SPI Flash interface

- eMMC interface

- SDMMC interface

- Support system code download by the following interface:

- USB OTG interface (Device mode)

- SPI interface (Slave mode)

- UART interface

- Support system boot from the following device:

- Internal SRAM

- 1024KB System SRAM

- 16KB PMU SRAM

- Integrated DDR is Different chip model will integrate different DDR capacity.

External Memory or Storage device

- Dynamic Memory Interface (DDR2/DDR3/DDR3L)

- Compatible with JEDEC standards

- Compatible with DDR2-1066/DDR3-1600/DDR3L-1600

- Support 16-bit data width

- Support 1 ranks (chip selects)

- Support max 1024MB addressing space

- Low power modes, such as power-down and self-refresh for SDRAM

- Serial Flash Interface

- Support transfer data from/to SPI flash device

- Support x1, x2, x4, x8 data bits mode

- Support SDR, DDR mode

- Support XIP (eXecute In Place)

- Support up to 1 chip select

- eMMC Interface

- Compatible with standard iNAND interface

- Compatible with eMMC specification 51

- Data bus width is 8bits

- SD/MMC/SDIO Interface

- Compatible with 0, MMC ver4.51, SDIO3.0 protocol

- Data bus width is 4bits

System Component

- CRU (clock & reset unit)

- One oscillator with external crystal input

- One internal low frequency RC clock

- One internal power on reset circuit

- Support single-end 768KHz clock input/output from/to GPIO

- Support PLL control and generate various clock frequency for chip

- Support clock gating control for individual components

- Support global soft-reset control for whole chip, also individual soft-reset for each component

- PMU(power management unit)

- Three separate digital voltage domains (DSP0_DVDD/CORE_DVDD/PMU_DVDD)

- Multiple configurable work sleep modes to save power consumption by different frequency or automatic clock gating control or external power on/off control

- Timer

- Twenty 64bits timers with interrupt-based operation

- One 64bits timer for low power mode application

- Support two operation modes: free-running and user-defined count

- Support timer work state checkable

- PWM

- 8-channels PWM with interrupt-based operation

- Support capture mode

- Provides reference mode and output various duty-cycle waveform

- Support continuous mode or one-shot mode

- Support one channel IR TX and one channel IR RX application

- Support one clock frequency calculation engine and one clock free running counter

- Support four channel waveform generation through lookup table

- Watchdog

- Support five 32-bit watchdog counter

- Counter counts down from a preset value to 0 to indicate the occurrence of a timeout

- WDT can perform two types of operations when timeout occurs:

- Generate a system reset

- First generate an interrupt and if this is not cleared by the service routine by the time a second timeout occurs then generate a system reset

- Programmable reset pulse length

- Totally 16 defined ranges of main timeout period

- Mailbox

- One Mailbox to service different core’s communication

- Support sixteen mailbox elements, each element includes one data word, one command word register and one flag bit that can represent one interrupt

- Spinlock

- Support spinlock registers for software to realize resource management

- DMA

- Support five embedded DMA controllers

- Support data transfer types with memory-to-memory, memory-to-peripheral, peripheral-to-memory

- Support TrustZone technology and programmable secure state for each DMA channel

- Support 8 channels for each DMA controller

- Secure System

- Cipher engine

- Support SHA-1, SHA-256/224, MD5 with hardware padding

- Support HMAC of SHA-1, SHA-256, MD5 with hardware padding

- Support AES-128, AES-192, AES-256 encrypt & decrypt cipher

- Support AES ECB/CBC/OFB/CFB/CTR/CTS/XTS/CCM/GCM/CBC-MAC/CMAC mode

- Support up to 4096 bits PKA mathematical operations for RSA

- Support two 256 bits RNG output

- Support secure boot

- Support secure debug

- Support secure OTP

- Support secure OS

- Support bus firewall

- Cipher engine

Video Output Processor

- Support RGB888/RGB565 source data format

- Support RGB888/RGB565/RGB666 display data format

- Support i8080 MCU serial interface

- Support max output resolution 480×480

Audio Interface

- SAI

- Support eight SAI components

- Support audio protocol: I2S, PCM, TDM

- Support up to 128 slots available with configurable size

- Support slot length 8 to 32 bits configurable

- Support slot valid data length 8 to 32 bits configurable

- SAI0/SAI4 support up to four lane transmitter and four lane parallel receiver

- SAI1/2/3/5/6/7 support up to two lane transmitter and two lane receiver

- Support combine different SAI component to meet more transmitter and receiver lane

- PDM

- Support PDM master receive mode

- Support 5 wire PDM interface with one is clock and 4 data line

- Support up to 8 mono microphones

- Support 16~24 bits sample resolution

- SPDIF

- Support SPDIF TX x 1

- Support SPDIF RX x 2

- Support 16bits/20bits/24bits resolution

- Support linear PCM mode (IEC-60958)

- Support non-linear PCM transfer (IEC-61937)

- ASRC

- Support eight ASRC components

- Support fixed length conversion mode and real time conversion mode

- Support asynchronous sample rate clock for real time conversion mode

- ASRC0/ASRC4 support 8 channel sample rate converter

- ASRC1/2/3/5/6/7 support 4 channel sample rate converter

- Support combine different ASRC component to meet more channel sample rate converter

Connectivity

- RMII 10/100 Ethernet Controller

- Support one Ethernet Controller

- Supports 10/100-Mbps data transfer rates with the RMII interfaces

- Supports both full-duplex and half-duplex operation

- USB 0 OTG

- Support one USB 0 OTG port

- Compatible with USB 0 specification

- Supports high-speed (480Mbps), full-speed (12Mbps) and low-speed (1.5Mbps) mode

- FLEXBUS interface

- Support transfer data from internal memory to GPIO by DMA

- Support transfer data from GPIO to internal memory by DMA

- Support multiple operating modes

- Multiplexing TX clock and RX clock, Multiplexing TX data and RX data

- Support TX only mode, RX only mode, TX then RX mode

- Multiplexing TX clock and RX clock, Separating TX data and RX data

- Support TX only mode, RX only mode, TX and RX mode, TX then RX mode

- Separating TX clock and RX clock, Separating TX data and RX data

- Support TX only mode, RX only mode, TX and RX mode

- Support clock free running mode and following data mode

- Support TX data width 2, 4, 8, 16 bit configurable

- Support RX data width 2, 4, 8, 16 bit configurable

- Support continue transmission mode and fix length transmission mode

- Support two chip selection function

- Support TX clock auto gating

- Support DVP (RGB888, RGB565, YUV422) interface for camera sensor

- Multiplexing TX clock and RX clock, Multiplexing TX data and RX data

- SPI interface

- Support three SPI Controllers

- SPI0 support serial-slave mode

- SPI1/SPI2 support serial-master and serial-slave mode, software-configurable

- I2C interface

- Support six I2C interface

- Support 7bits and 10bits address mode

- Software programmable clock frequency

- Data on the I2C-bus can be transferred at rates of up to 100 Kbit/s in the Standard-mode, up to 400 Kbit/s in the Fast-mode or up to 1 Mbit/s in Fast-mode Plus

- UART Controller

- Support four UART interface

- Embedded two 64-byte FIFO for TX and RX operation respectively

- Support 5bit, 6bit, 7bit, 8bit serial data transmit or receive

- Standard asynchronous communication bits such as start, stop and parity

- Support different input clock for UART operation to get up to 4Mbps baud rate

- Support auto flow control mode

- CAN Controller

- Support one CAN interface

- Support CAN 0B protocol

- Support transmit or receive standard frame

- Support transmit or receive extended frame

- Touch Key Controller

- Support muti-channel CapSense monitor

- Support trigger interrupt waterline configurable

- Support LPF and DC elimination

Others

- Multiple groups of GPIO

- All of GPIOs can be used to generate interrupt

- Support level trigger and edge trigger interrupt

- Support configurable polarity of level trigger interrupt

- Support configurable rising edge, falling edge and both edge trigger interrupt

- Support configurable pull direction (pullup or pulldown)

- Support configurable drive strength

- Support configurable slew rate

- Temperature Sensor (TS-ADC)

- Up to 50KS/s sampling rate

- Support one temperature sensor

- -40~125℃ temperature range and 5℃ temperature resolution

- Successive Approximation ADC (SARADC)

- 10-bit resolution

- Up to 1MS/s sampling rate

- 4 single-ended input channels

- GPIO multiplexed

- OTP

- Support 8K bits Size, 7K bit for secure application

- Support Program/Read/Idle mode

- Package Type

- RK2118G: QFP128L(body: 14mm x 14mm; lead pitch: 4mm)

- Support MCP 512Mb DDR