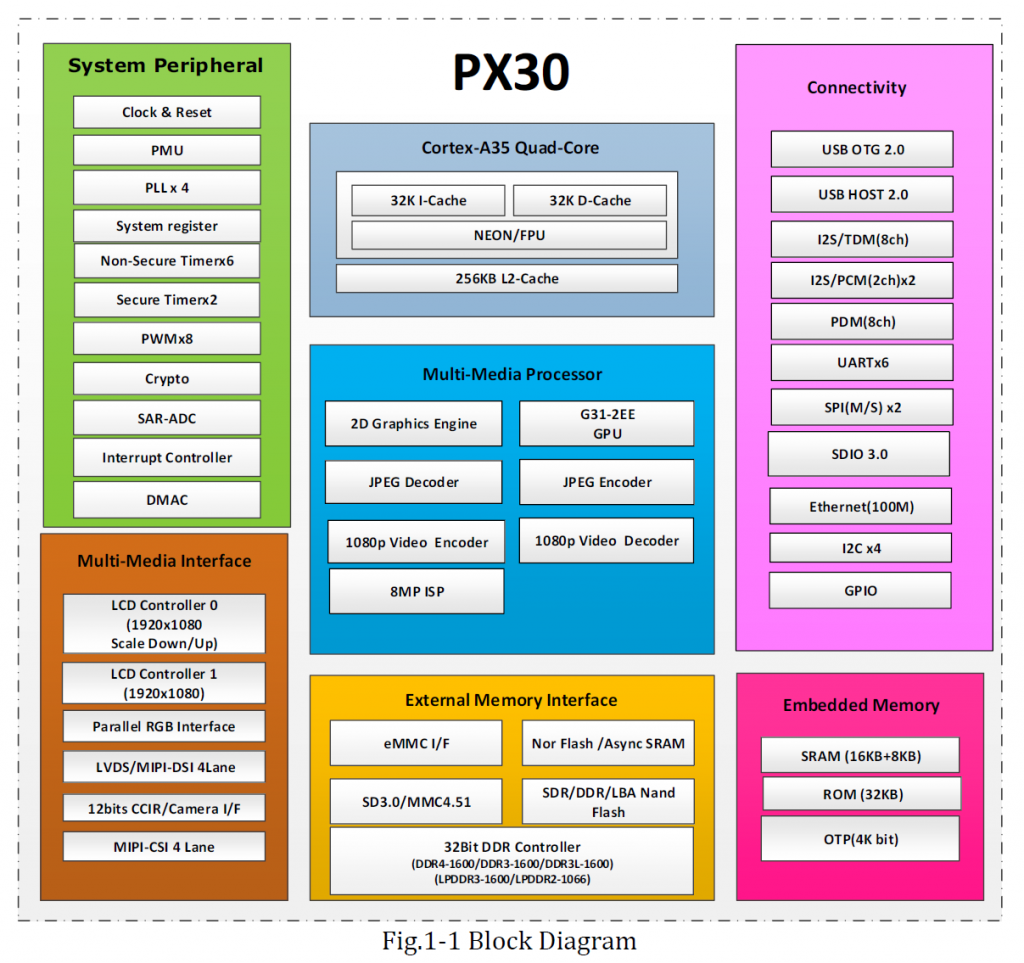

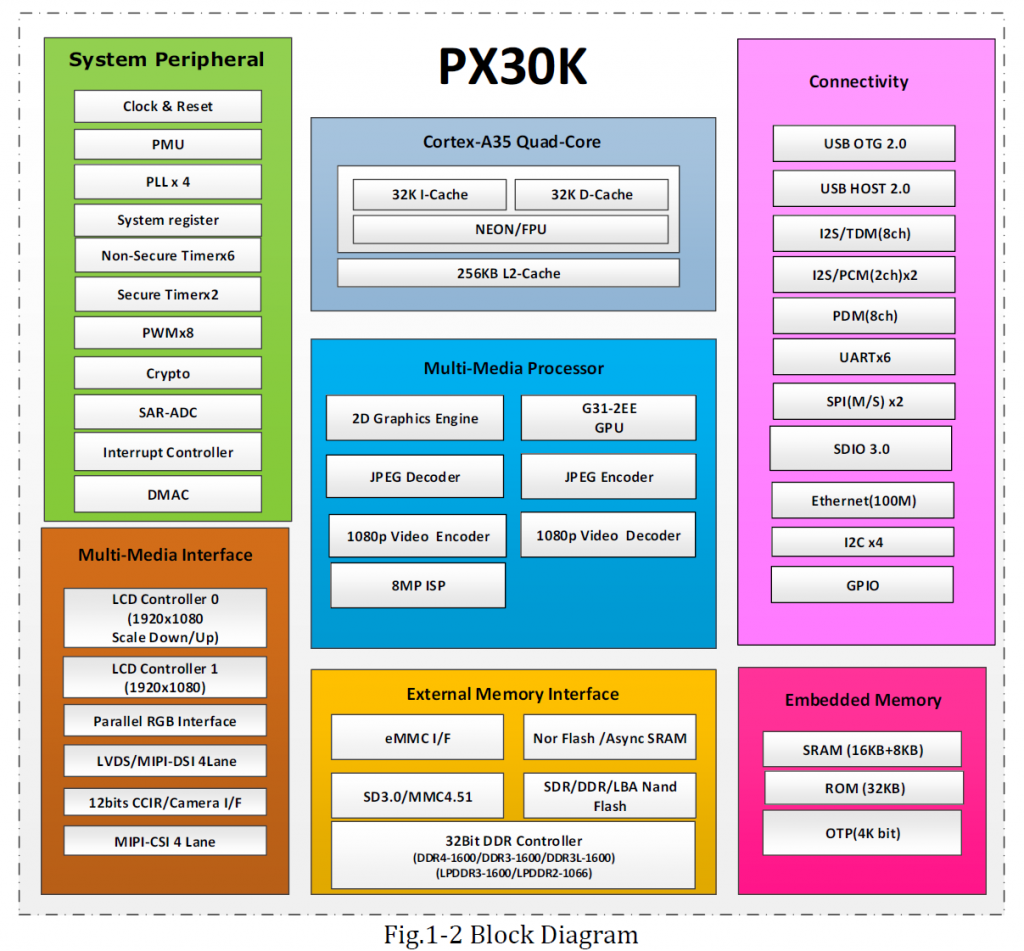

Rockchip PX30/PX30K 芯片简介

1.1 Overview

PX30 is a high-performance Quad-core application processor designed for personal mobile internet device and other digital multimedia applications.

Many embedded powerful hardware engines are provided to optimize performance for high- end application. PX30 supports almost full-format H.264 decoder by 1080p@60fps, H.265 decoder by 1080p@60fps, also support H.264 encoder by 1080p@30fps, high-quality JPEG encoder/decoder.

Embedded ARM G31-2EE GPU makes PX30 completely compatible with OpenGL ES 1.1/2.0/3.2, DirectX 11 FL9_3, OpenCL 2.0 and Vulkan 1.0 Special 2D hardware engine will maximize display performance and provide very smoothly operation.

PX30 has high-performance external memory interface (DDR3/DDR3L/DDR4/LPDDR2/LPDDR3) capable of sustaining demanding memory bandwidths.

1.2 Features

1.2 Features

The features listed below which may or may not be present in actual product, may be subject to the third party licensing requirements. Please contact Rockchip for actual product feature configurations and licensing requirements.

1.2.1 Microprocessor

- Quad-core ARM Cortex-A35 CPU

- Full implementation of the ARM architecture v8-A instruction set

- ARM Neon Advanced SIMD (single instruction, multiple data) support for accelerated media and signal processing computation

- ARMv8 Cryptography Extensions

- In-order pipeline with symmetric dual-issue of most instructions

- 256KB unified system L2 cache

- Include VFP v3 hardware to support single and double-precision operations

- Integrated 32KB L1 instruction cache, 32KB L1 data cache with 4-way set associative

- TrustZone technology support

- Separate power domains for CPU core system to support internal power switch and externally turn on/off based on different application scenario

- PD_A35_0: 1st Cortex-A35 + Neon + FPU + L1 I/D Cache

- PD_A35_1: 2nd Cortex-A35 + Neon + FPU + L1 I/D Cache

- PD_A35_2: 3rd Cortex-A35 + Neon + FPU + L1 I/D Cache

- PD_A35_3: 4th Cortex-A35 + Neon + FPU + L1 I/D Cache

- One isolated voltage domain to support DVFS

1.2.2 Memory Organization

1.2.2 Memory Organization

- Internal on-chip memory

- BootROM

- SYSTEM_SRAM in the voltage domain of VD_LOGIC

- PMU_SRAM in the voltage domain of VD_PMU for low power application

- External off-chip memory①

- DDR3/DDR3L/DDR4/LPDDR2/LPDDR3

- SPI Flash

- eMMC

- SD_Card

- 8bits Async Nand Flash

- 8bits toggle Nand Flash

- 8bit ONFI Nand Flash

1.2.3 Internal Memory

- Internal BootRom

- Support system boot from the following device:

- SPI Flash interface

- eMMC interface

- SDMMC interface

- Toggle Nand Flash

- Async Nand FLash

- Support system code download by the following interface:

- USB OTG interface (Device mode)

- Support system boot from the following device:

- SYSTEM_SRAM

- Size: 16KB

- PMU_SRAM

- Size: 8KB

1.2.4 External Memory or Storage device

- Dynamic Memory Interface (DDR3/DDR3L/DDR4/LPDDR2/LPDDR3)

- Compatible with JEDEC standards

- Compatible with DDR3-1600/DDR3L-1600/DDR4-1600/LPDDR2-1066 /LPDDR3- 1600

- Support 32-bit data width, 2 ranks (chip selects), max 4GB addressing space per rank; total addressing space is 4GB(max) also

- Low power modes, such as power-down and self-refresh for SDRAM

- Compensation for board delays and variable latencies through programmable pipelines

- Programmable output and ODT impedance with dynamic PVT compensation

- eMMC Interface

- Compatible with standard iNAND interface

- Compatible with eMMC specification 4.41, 4.51, 5.0 and 1

- Support three data bus width: 1-bit, 4-bit or 8-bit

- Support up to HS200; but not support CMD Queue

- SD/MMC Interface

- Compatible with SD3.0, MMC 51

- Data bus width is 4bits

- Nand Flash Interface

- Support async nand flash, each channel 8bits, up to 4 banks

- Support ONFI Synchronous Flash Interface, each channel 8bits, up to 4 banks

- Support Toggle Flash Interface, each channel 8bits, up to 4 banks

- Support LBA nand flash in async or sync mode

- Up to 70bits/1KB hardware ECC

- For DDR nand flash, support DLL bypass and 1/4 or 1/8 clock adjust, maximum clock rate is 75MHz

- For async nand flash, support configurable interface timing , maximum data rate is 8bit/cycle

1.2.5 System Component

- CRU (clock & reset unit)

- Support clock gating control for individual components

- One oscillator with 24MHz clock input

- Support global soft-reset control for whole chip, also individual soft-reset for each component

- PMU(power management unit)

- 3 separate voltage domains(VD_CORE/VD_LOGIC/VD_PMU)

- 14 separate power domains, which can be power up/down by software based on different application scenes

- Multiple configurable work modes to save power by different frequency or automatic clock gating control or power domain on/off control

- Timer

- Six 64bits timers with interrupt-based operation for non-secure application

- Two 64bits timers with interrupt-based operation for secure application

- Support two operation modes: free-running and user-defined count

- Support timer work state checkable

- PWM

- Eight on-chip PWMs(PWM0~PWM7) with interrupt-based operation

- Programmable pre-scaled operation to bus clock and then further scaled

- Embedded 32-bit timer/counter facility

- Support capture mode

- Support continuous mode or one-shot mode

- Provides reference mode and output various duty-cycle waveform

- Optimized for IR application for PWM3 and PWM7

- Watchdog

- 32-bit watchdog counter

- Counter counts down from a preset value to 0 to indicate the occurrence of a timeout

- WDT can perform two types of operations when timeout occurs:

- Generate a system reset

- First generate an interrupt and if this is not cleared by the service routine by the time a second timeout occurs then generate a system reset

- Programmable reset pulse length

- Totally 16 defined-ranges of main timeout period

- One Watchdog for non-secure application

- One Watchdog for secure application

- Interrupt Controller

- Support 3 PPI interrupt source and 128 SPI interrupt sources input from different components

- Support 16 software-triggered interrupts

- Two interrupt outputs (nFIQ and nIRQ) separately for each Cortex-A35, both are low-level sensitive

- Support different interrupt priority for each interrupt source, and they are always software-programmable

- DMAC

- Micro-code programming based DMA

- The specific instruction set provides flexibility for programming DMA transfers

- Linked list DMA function is supported to complete scatter-gather transfer

- Support internal instruction cache

- Embedded DMA manager thread

- Support data transfer types with memory-to-memory, memory-to-peripheral, peripheral-to-memory

- Signals the occurrence of various DMA events using the interrupt output signals

- Mapping relationship between each channel and different interrupt outputs is software-programmable

- One embedded DMA controller for system

- DMAC features:

- 8 channels totally

- 23 hardware request from peripherals

- 2 interrupt output

- Dual APB slave interface for register configuration, designated as secure and non-secure

- Support trustzone technology and programmable secure state for each DMA channel

- Secure system

- TrustZone based Trusted Execution Environment (TEE) for the following components

- Cortex-A35, support security and non-security mode, switch by software

- System general DMAC, support some dedicated channels work only in security mode

- Secure OTP, only can be accessed by Cortex-A35 in secure mode and secure key reader block

- SYSTEM_SRAM, part of space is addressed only in security mode, detailed size is software-programmable together with TZMA (TrustZone memory adapter)

- eight secure address space in DDR device, the start address and end address for each address scope is configurable, maximum 4GB secure address are supported

- Cipher engine

- Support SHA-1, SHA-256/224, SHA-512/384, MD5 with hardware padding

- Support HMAC of SHA-1, SHA-256, SHA-512, MD5 with hardware padding

- Support AES-128, AES-192, AES-256 encrypt & decrypt cipher

- Support DES & TDES cipher

- Support AES ECB/CBC/OFB/CFB/CTR/CTS/XTS/CCM/GCM/CBC-MAC/CMAC mode

- Support DES/TDES ECB/CBC/OFB/CFB mode

- Support up to 4096 bits PKA mathematical operations for RSA/ECC

- Support hardware key loader from secure OTP, which is not accessable by other devices, including Cort4ex-A35

- Support data scrambling for DDR3/DDR3L/DDR4/LPDDR2/LPDDR3

- Support up to 256 bits TRNG Output

- Support secure OTP

- Support secure boot

- Support secure debug

- TrustZone based Trusted Execution Environment (TEE) for the following components

1.2.6 Video CODEC

- Video Decoder

- Real-time decoding of MPEG-4, H.264, H.265/HEVC, VP8, VC-1

- 264/AVC Base/Main/High@level4.2; up to 1080P@60fps

- 265/HEVC Main10 profile@level4.2; up to 1080P@60fps

- VP8, up to 1080P@60fps

- MPEG-4, ISO/IEC 14496-2, SP@L0-3, ASP@L0-5, up to 1080P@60fps

- VC-1, SP@ML, MP@HL, AP@L0-3, up to 1080P@60fps

- MVC is supported based on H.264 or H.265, up to 1080P@60fps

- Video Encoder

- Support H.264 video encoder at BP/MP/HP@level4.1

- Resolution and frame rate are up to 1920×1080@30FPS

- 1x1080p@30fps or 2x720p@30fps encoding

1.2.7 JPEG CODEC

- JPEG decoder

- Decoder size is from 48×48 to 8176×8176(66.8Mpixels)

- Support JPEG ROI (region of image) decode

1.2.8 Graphics Engine

- 3D Graphics Engine:

- Support DirectX 11 FL9_3

- Support OpenGL ES 1.1, 2.0, and 2

- Support Vulkan 0

- Support OpenCL 2.0 Full Profile

- 2D Graphics Engine:

- Data format

- Support input of ARGB/RGB888/RGB565/RGB4444/RGB5551/YUV420/YUV422

- Support input of YUV422SP10bit/YUV420SP10bit(YUV-8bits out)

- Support output of ARGB/RGB888/RGB565/RGB4444/RGB5551/YUV420/YUV422

- Pixel Format conversion, 601/BT.709

- Dither operation

- Max resolution: 8192×8192 source, 4096×4096 destination

- Scaling

- Down-scaling: Average filter

- Up-scaling: Bi-cubic filter(source>2048 would use Bi-linear)

- Arbitrary non-integer scaling ratio,from 1/8 to 8

- Rotation

- 0, 90, 180, 270 degree rotation

- x-mirror, y-mirror& rotation operation

- BitBLT

- Block transfer

- Color palette/Color fill, support with alpha

- Transparency mode (color keying/stencil test, specified value/value range)

- Two source BitBLT:

- A+B=B only BitBLT, A support rotate&scale when B fixed

- A+B=C second source (B) has same attribute with (C) plus rotation function

- Alpha Blending

- New comprehensive per-pixel alpha(color/alpha channel separately)

- Fading

- SRC1(R2Y)&&SRC0(YUV)—alpha->DST(YUV)

- Data format

1.2.9 Video input interface

- Interface and video input processor

- Support up to 12bit DPI interface (digital parallel input)

- Support up MIPI CSI RX interface

- Support VIP block(Video Input Processor)

- Support ISP block(Image Signal Processor)

- Support DPI interface to VIP block

- Support DPI interface to ISP block

- Support MIPI CSI RX interface to ISP block

- Support the following two mode simultaneously

- DPI interface with VIP

- MIPI CSI RX interface with ISP

- DPI Interface

- Support 8bit/10bit/12bit input

- Support up to 150MHz input data

- Support 12MHz/24MHz/48MHz/27MHz/37.125MHz/74.25MHz frequency for master clock output

- MIPI CSI RX Interface

- Compatible with the MIPI Alliance Interface specification 0

- Up to 4 data lane, 1.0Gbps maximum data rate per lane

- Support MIPI-HS, MIPI-LP mode

- VIP

- Support YCbCr422 8bit input

- Support Raw 8bit/10bit/12bit input

- Support CCIR656(PAL/NTSC) input

- Support JPEG input

- Support YCbCr422/420 output

- Support UYVY/VYUY/YUYV/YVYU configurable

- Support up to 8192×8192 resolution source

- Support picture in picture

- Support arbitrary size window crop

- ISP

- Generic Sensor Interface with programmable polarity for synchronization signals

- ITU-R BT 601/656 compliant video interface supporting YCbCr or RGB Bayer data

- 12 bit camera interface

- 12 bit resolution per color component internally

- YCbCr 4:2:2 processing

- Flash light control

- Mechanical shutter support

- Windowing and frame synchronization

- Frame skip support for video (e.g. MPEG-4) encoding

- Macro block line, frame end, capture error, data loss interrupts and sync. (h_start, v_start) interrupts

- Luminance/chrominance and chrominance blue/red swapping for YUV input signals

- Continuous resize support

- Semi planar storage format

- Color processing (contrast, saturation, brightness, hue, offset, range)

- Power management by software controlled clock disabling of currently not needed sub-modules

- Four channel Lens shade correction (Vignetting)

- Auto focus measurement

- White balancing and black level measurement

- Auto exposure support by brightness measurement in 5×5 sub windows

- Defect pixel cluster correction unit (DPCC) supports on the fly and table based pixel correction

- De-noising pre filter (DPF)

- Enhanced color interpolation (RGB Bayer demosaicing)

- Chromatic aberration correction

- Combined edge sensitive Sharpening / Blurring filter (Noise filter)

- Color correction matrix (cross talk matrix)

- Global Tone Mapping with wide dynamic range unit (WDR)

- Image Stabilization support and Video Stabilization Measurement

- Flexible Histogram calculation

- Digital image effects (Emboss, Sketch, Sepia, B/W (Grayscale), Color Selection, Negative image, sharpening)

- Solarize effect through gamma correction

- Maximum input resolution of 3264×2448 pixels

- Main scaler with pixel-accurate up- and down-scaling to any resolution between

3264×2448 and 32×16 pixel in processing mode

- Self scaler with pixel-accurate up- and down-scaling to any resolution between 1920×1080 and 32×16 pixel in processing mode

- Support of semiplanar NV21 color storage format

- Support of image cropping

- Support Y12BIT and UV 8BIT path output after GAMMAOUT module

- Support RGB output after GAMMAOUT module

- Support hurry for latency FIFO

- Support Two-in-one RK-Tone-Mapping with wide dynamic range unit (Block/Global WDR)

- Support Video Stabilization Measurement (VSM) Programming update to 3264×2448

1.2.10 Display interface

- Display interface

- Support RGB Parallel Display interface

- Support MIPI_DSI interface

- Support LVDS interface

- Support Parallel Display interface and MIPI_DSI display simultaneously

- Support Parallel Display interface and LVDS display simultaneously

- Support different or identical source for dual display interface

- RGB Parallel Display interface

- Up to 100MHz display output

- Up to 24bit output data

- MIPI_DSI interface

- Compatible with MIPI Alliance Interface specification 0

- Support 4 data lane, 1.0Gbps maximum data rate per lane

- Up to 1080p@60fps display output

- Support HS and LP mode

- LVDS interface

- Compliant with the TIA/EIA-644-A LVDS specification

- Compliant with LVTTL IO, support direct RGB data output

- Support RGB888 and RGB666 for LVDS interface

- Support VESA/JEIDA LVDS data format transfer

- Up to 1280×800@60fps

1.2.11 Big Video Output Processor (VOPB)

- Display interface

- Parallel RGB LCD Interface: 24-bit(RGB888),18-bit(RGB666), 16-bit(RGB565)

- Max output resolution

- Up to 1920×1080 with CABC disable

- Up to 1280×800 with CABC enable

- Display process

- Background layer

- programmable 24-bit color

- Win0 layer

- Input format : RGB888, ARGB888, RGB565, YCbCr422, YCbCr420, YCbCr444

- 1/8 to 8 scaling-down and scaling-up engine

- Support virtual display

- 256 level alpha blending (pre-multiplied alpha support)

- Transparency color key

- YCbCr2RGB(rec601-mpeg/ rec601-jpeg/rec709)

- RGB2YCbCr(BT601/BT709)

- Background layer

- Win1 layer

- Input format : RGB888, ARGB888, RGB565

- Support virtual display

- 256 level alpha blending (pre-multiplied alpha support)

- Transparency color key

- RGB2YCbCr(BT601/BT709)

- Support frame buffer data decompression

- HWC layer

- Support 8BPP only

- Size : 32×32 or 64×64

- 256 level alpha blending (pre-multiplied alpha support)

- RGB2YCbCr(BT601/BT709)

- Others

- Win0 layer , Win1 layer and Win2 layer overlay exchangeable

- Support RGB or YUV domain overlay

- BCSH(Brightness, Contrast, Saturation, Hue adjustment)

- BCSH:YCbCr2RGB(rec601-mpeg/ rec601-jpeg/rec709)

- BCSH:RGB2YCbCr(BT601/BT709)

- Support Gamma adjust

- Support CABC (Content Adaptive Backlight Control)

- Support dither down allegro RGB888to666 RGB888to565 & dither down frc (configurable ) RGB888to666

- Blank and black display

- Standby mode

1.2.12 Little Video Output Processor(VOPL)

- Display interface

- Parallel RGB LCD Interface: 24-bit(RGB888),18-bit(RGB666), 16-bit(RGB565)

- Max output resolution

- Up to 1920×1080

- Display process

- Background layer

- programmable 24-bit color

- Win1 layer

- Input format : RGB888, ARGB888, RGB565

- Support virtual display

- 256 level alpha blending (pre-multiplied alpha support)

- Transparency color key

- RGB2YCbCr(BT601/BT709)

- Others

- Support RGB or YUV domain overlay

- BCSH(Brightness, Contrast, Saturation, Hue adjustment)

- BCSH:YCbCr2RGB(rec601-mpeg/rec601-jpeg/rec709)

- BCSH:RGB2YCbCr(BT601/BT709)

- Support Gamma adjust

- Support dither down allegro RGB888to666 RGB888to565 & dither down for (configurable ) RGB888to666

- Blank and black display

- Standby mode

- Background layer

1.2.13 Audio Interface

- I2S0 with 8 channel

- Up to 8 channels TX and 8 channels RX path

- Audio resolution from 16bits to 32bits

- Sample rate up to 192KHz

- Provides master and slave work mode, software configurable

- Support 3 I2S formats (normal, left-justified, right-justified)

- Support 4 PCM formats (early, late1, late2, late3)

- I2S and PCM mode cannot be used at the same time

- I2S1/I2S2 with 2 channel

- Up to 2 channels for TX and 2 channels RX path

- Audio resolution from 16bits to 32bits

- Sample rate up to 192KHz

- Provides master and slave work mode, software configurable

- Support 3 I2S formats (normal, left-justified, right-justified)

- Support 4 PCM formats (early, late1, late2, late3)

- I2S and PCM cannot be used at the same time

- PDM

- Up to 8 channels

- Audio resolution from 16bits to 24bits

- Sample rate up to 192KHz

- Support PDM master receive mode

- TDM

- supports up to 8 channels for TX and 8 channels RX path

- Audio resolution from 16bits to 32bits

- Sample rate up to 192KHz

- Provides master and slave work mode, software configurable

- Support 3 I2S formats (normal, left-justified, right-justified)

- Support 4 PCM formats (early, late1, late2, late3)

1.2.14 Connectivity

- SDIO interface

- Compatible with SDIO3.0 protocol

- 4bits data bus widths

- MAC 10/100 Ethernet Controller

- Supports 10/100-Mbps data transfer rates with the RMII interfaces

- Supports both full-duplex and half-duplex operation

- Supports IEEE 802.1Q VLAN tag detection for reception frames

- Support detection of LAN wake-up frames and AMD Magic Packet frames

- Handles automatic retransmission of Collision frames for transmission

- USB 2.0 OTG

- Compatible with USB 2.0 specification

- Supports high-speed(480Mbps), full-speed(12Mbps) and low-speed(1.5Mbps) mode

- USB 2.0 Host

- Compatible with USB 2.0 specification

- Supports high-speed(480Mbps), full-speed(12Mbps) and low-speed(1.5Mbps) mode

- Support Enhanced Host Controller Interface Specification (EHCI), Revision 0

- Support Open Host Controller Interface Specification (OHCI), Revision 0a

- SPI interface

- Support two SPI Controller, one support one chip-select output and the other support two chip-select output

- Support serial-master and serial-slave mode, software-configurable

- I2C interface

- Support four I2C interface(I2C0/I2C1/I2C2/I2C3)

- Support 7bits and 10bits address mode

- Software programmable clock frequency

- Data on the I2C-bus can be transferred at rates of up to 100 kbit/s in the Standard- mode, up to 400 kbit/s in the Fast-mode or up to 1 Mbit/s in Fast-mode

- UART Controller

- Support six UART interface(UART0/UART1/UART2/UART3/UART4/UART5)

- Embedded two 64-byte FIFO for TX and RX operation respectively

- Support 5bit,6bit,7bit,8bit serial data transmit or receive

- Standard asynchronous communication bits such as start, stop and parity

- Support different input clock for UART operation to get up to 4Mbps baud rate

- Support auto flow control mode for UART0/UART1/UART3/UART4/UART5

1.2.15 Others

- Multiple group of GPIO

- All of GPIOs can be used to generate interrupt to CPU

- Support level trigger and edge trigger interrupt

- Support configurable polarity of level trigger interrupt

- Support configurable rising edge, falling edge and both edge trigger interrupt

- Temperature Sensor(TS-ADC)

- Up to 50KS/s sampling rate

- Support two temperature sensor

- -20~120℃ temperature range and 5℃ temperature resolution

- Successive Approximation ADC (SARADC)

- 10-bit resolution

- Up to 1MS/s sampling rate

- 3 single-ended input channels

- OTP

- Support 4K bit Size, 3.5K bit for secure application

- Support Program/Read/Idle mode

- Package Type

TFBGA418L (body: 14mm x 14mm; ball size: 0.3mm; ball pitch: 0.65mm)