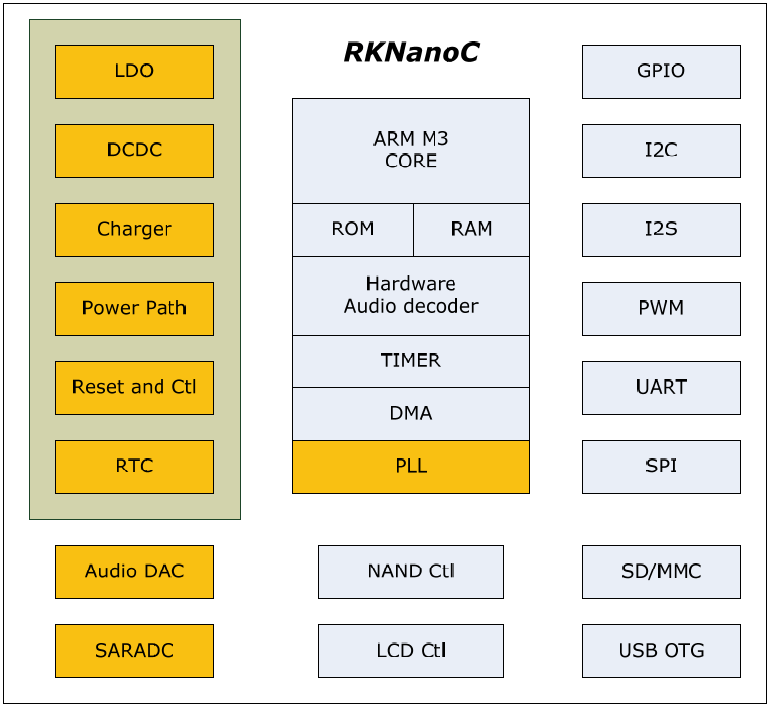

RKNanoC是一种低成本、低功耗、高效率的数字多媒体芯片SoC,它基于ARM低功耗处理器架构,并配有硬件加速器。它专为便携式音频产品应用而设计,如MP3播放器等。RKNanoC可以支持各种类型的音频标准解码,如MP3/WMA/OGG/FLAG/AAC等。由于内置音频硬件加速器,RKNanoC可以在极低的系统频率下实现音频解码,这可以节省芯片功耗。通过提供一整套外围接口,RKNanoC可以支持非常灵活的应用,包括NAND闪存、LCDC、USB OTG、SD/MMC、I2C、I2S、SPI、UART、PWM等。

2. Features

System Operation

ARM processor

AHB-lite bus connection

Selectable booting method

Boot from NAND FLASH

Boot from eMMC flash

Boot from SPI NOR flash

Memory Organization

Internal 224KB SRAM for IRAM and DRAM

Embedded 64KB ROM for decoder and system code

Processor

ARM Cortex-M3 low power core

A Thumb instruction set subset

Banked Stack Pointer (SP) only

Hardware divide instructions, SDIV and UDIV (Thumb 32-bit instructions)

Handler and Thread modes

Thumb and Debug states

Interruptible-continued LDM/STM, PUSH/POP for low interrupt latency

Automatic processor state saving and restoration for low latency Interrupt

Service Routine (ISR) entry and exit

Nested Vectored Interrupt Controller (NVIC)

26 external interrupts.

8-level priority of interrupt

Clock & Power Management

One on-chip PLL, system main clock can be PLL clock or OSC input clock

Support different main clock and internal AHB Bus clock ratio:

1:1, 1:2, 1:3, 1:4, up to 1:8 modes

Support different AHB Bus clock and ARM system tick clock ratio:

1:2, 1:3, 1:4, up to 1:8 modes

Support different AHB Bus clock and ARM APB Bus clock ratio:

1:1, 1:2, 1:3 and 1:4 mode

100MHz Max frequency for ARM Core

Clock gating for ARM Cortex-M3 sleep mode and other peripherals

RKnanoC Datasheet Rockchip Confidential

5 4/3/2013

Support ARM clock bypass/divider 2/divider 4 path for 24MHz arm clock

Hardware Accelerator for MP3 decode

MP3 imdct36 calculation module

MP3 subband synthesize module

Memory Interface

External-Memory controller

Support 4 chip selects for NAND flash

Support 24/40/60bits ECC error correction

Support 8bits data-width to external NAND

SD/MMC controller

SD/MMC SPI mode/1bit mode/4bit mode

Support Multi Media Card Specification Version 4.41

Support SD Memory Card Specification Version 3.0

Support Secure Digital I/O(SDIO Version3.0)

Cards Clock Rate up to PCLK, Re-scaling the SD/MMC clock (PCLK) with the

8-bits pre-scale register in SCU block

VIDEO interface

LCD controller

Compatible with MCU LCD Panel

Up to 8 LCD data output bus

DMA Controller

One DMA Controller in chip

Support 3 DMA channels, 7 external requests

Support incremental and fixed addressing mode

Support hardware and software trigger DMA transfer mode

Support error interrupt, transport-complete interrupt

When transport data is not align with source burst, the last data will be

transported in single burst mode

Support configurable channel priority

USB interface

USB 2.0 OTG controller and PHY

Operates in High-Speed and Full-Speed mode

Support Session Request Protocol(SRP) and Host Negotiation Protocol(HNP)

Support 6 endpoints , one control endpoint, two IN/OUT endpoints, one IN

endpoint

Support 4 channels at Host mode, support bulk transfer

Low speed Peripheral interface

I2C controller

Supports master and slave modes of I2C bus

Software programmable clock frequency and transfer rate up to 100Kbit/s in

standard mode or up to 400Kbit/s in Fast mode

Supports 7 bits and 10 bits addressing modes

RKnanoC Datasheet Rockchip Confidential

6 4/3/2013

I2S

Support mono/stereo audio file

Support audio resolution: 8, 16 bits

Support audio sample rate from 8KHz to 48 KHz

Support I2S, Left-Justified and Right-Justified digital serial data format

PWM

3 Channels Built-in 16 bit timer

0 ~ 100 % duty ratio PWM signal generation

Re-scaling the counting clock ( PCLK) with the 8-bits pre-scale register in SCU

block

SPI master

Serial-master operation – Enables serial communication with serial-slave

peripheral devices.

DMA Controller Interface – Enables interface to a DMA controller using a

handshaking interface for transfer requests.

Support interrupt interface to interrupt controller, and independently masking

of interrupts.

One hardware slave-select lines.

Dynamic control of the serial bit rate of the data transfer.

GPIO

Support 28 individually programmable input/output pins

28 GPIOs with external interrupt capability

Timer

Built-in One 24-bits timer module

Support for two operation modes : free-running and user-defined count

Uart

AMBA APB interface – Allows for easy integration into a Synthesizable

Components for AMBA 2 implementation.

DMA Controller Interface – Enables interface to a DMA controller over the AMBA

bus using a handshaking interface for transfer requests.

Support interrupt interface to interrupt controller.

Analog IP interface

AUDIO-DAC

24bit Audio DAC with Headphone Amplifier

Ultra Low Quiescent Current

Pop Noise free

High Efficiency Class G Headphone Amplifier

Asynchronous adopting different sampling rate

MIC amplifier

◆ 20DB low noise boost amplifier

◆ Low noise programmed amplifier for MIC input

ADC Converter

4-channel single-ended 10-bit 1MSPS Successive Approximation Register (SAR)

analog-to-digital converter

DCDC

1.2V Default Output Voltage setting RKnanoC Datasheet Rockchip Confidential 7 4/3/2013

Current mode control with Internal Compensation

100mA Output Current

Forced PWM operation

Adjustable output voltage.

3MHz operating frequency.

Integrated COUT discharge Switch.

LDO

3.3V Default Output Voltage

Stable with 0.8uF low ESR ceramic capacitor

100mA Output Current limit

Adjustable output voltage.

Integrated COUT discharge Switch

RTC

Working at 32.768KHz oscillator clock

16 bits compensation.

Power Manager Unit

On/Off Logic for power up/down control

Power on reset

Power on sequence control

Power path, switch power supply between battery and USB/AC adaptor input

Max 200mA charger, Charges Single Cell Li-lon Batteries Directly from USB prot

Package

NanoC LQFP80

NanoC-L LQFP64

NanoC-G TFBGA81

Rockchip RKnanoC datasheet V1.7