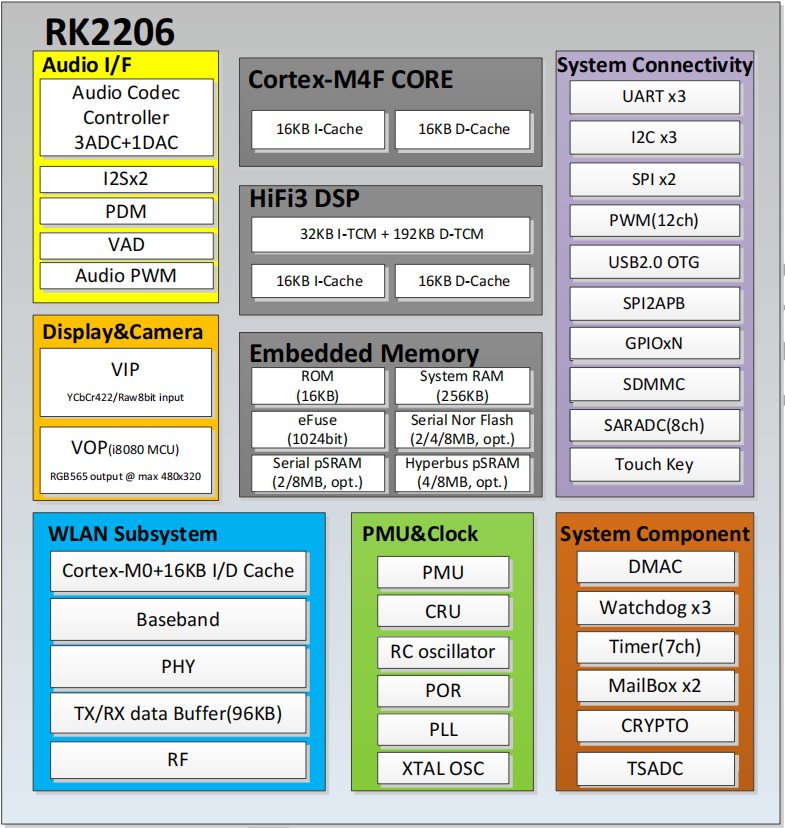

RK2206是一款低功耗、高集成度、基于单片机的无线局域网处理器。它可以应用于不同的应用领域,如物联网(IoT)、可穿戴设备、家庭自动化、云连接等。RK2206将Cortex-M4F与I/D缓存集成,以运行操作系统和应用程序。Cortex-M0带I/D缓存,可用于运行WLAN MAC堆栈。HiFi3 DSP可用于运行音频和智能语音交互相关算法。集成的480KB系统内存和就地执行(XIP)闪存/pSRAM接口使RK2206能够灵活地适应不同的应用程序开发。多芯片封装(MCP)可根据应用要求提供不同容量的片上闪存和pSRAM。

RK2206支持802.11b/g/n无线电和全媒体访问控制WLAN总体解决方案,集成了PA、发送/接收交换机、Balun、LNA,从而降低了BOM成本。开放式办公环境中优化的高吞吐量使互联网应用更加顺畅。支持自动硬件校准解决方案,以调整射频特性,实现最佳射频性能,避免因硬件板差异而造成的射频性能损失。搭载RK812 ASIC使用,为音频播放和智能语音交互应用提供单通道DAC和三通道ADC。丰富的外围设备,如USB2。0OTG、I2C、UART、PWM、SPI、CapSense、I2S、PDM、i8080显示接口、摄像头串行接口等,使产品开发更加简单多样。

搭载RK812 ASIC使用,直接支持电池供电,无需外部调节器,节省BOM成本。嵌入式语音活动检测功能可随时监控人声,及时响应人声请求,快速设置智能语音交互应用,降低硬件系统功耗,提高电池续航能力。

1.2 Features

The features listed below which may or may not be present in actual product, may be subject to the third party licensing requirements. Please contact Rockchip for actual product feature configurations and licensing requirements.

1.2.1 Cortex-M4F Microprocessor

The processor implements the ARMv7-M Thumb instruction set

Support floating point unit (FPU)

Nested Vectored Interrupt Controller (NVIC) closely integrated with the processor core to achieve low latency interrupt processing

Support memory protection unit (MPU)

Serial wire debug port (SW-DP) debug access

16KB I-Cache and 16KB D-Cache

2-way set associative

256 bit Cache line

1.2.2 Cortex-M0 Microprocessor

The processor implements the ARMv6-M Thumb instruction set

Nested Vectored Interrupt Controller (NVIC) closely integrated with the processor core to achieve low latency interrupt processing

Serial wire debug port (SW-DP) debug access

RK2206 Datasheet Rev 1.1

16KB I/D Cache

2-way set associative

256 bit Cache line

1.2.3 DSP

HiFi3 with 4 24-bit MAC or dual 32-bit MAC architecture

3 VLIW slots, 2-Way SIMD Vector FPU

Voice noise reduction optimization

Integrated 32KB/192KB I/D TCM

Integrated 16KB/16KB I/D Cache

1.2.4 Memory Organization

Internal on-chip memory

BootROM

Internal SRAM

eFuse

External off-chip memory

SD Card

Memory device by Multiple Chip Package(MCP)

MCP with Serial Nor Flash by Flexible Serial Peripheral Interface(FSPI)

Support transfer data from/to serial flash device

Support x1,x2,x4 data bits mode

Support XIP(eXecute In Place)

Support 1 chip select

Support 2MB/4MB/8MB optional capacity

MCP with Serial pSRAM by Flexible Serial Peripheral Interface(FSPI)

Support transfer data from/to pSRAM device

Support x1,x2,x4 data bits mode

Support 1 chip select

Support 2MB/8MB optional capacity

MCP with HyperBus pSRAM

Support transfer data from/to HyperBus pSRAM device

Support 8 data bits mode

Support DDR mode

Support 1 chip select

Support 2MB/4MB/8MB optional capacity

1.2.5 Internal Memory

Internal BootROM

Support system boot from the following device:

FSPI Nor Flash interface

SDMMC interface

Support system code download by the following interface:

USB OTG interface (Device mode)

SPI interface(Slave mode)

Internal SRAM

256KB system memory

Partial DSP TCM memory can be switched as system memory by software configurable

eFuse

Support 1K bit Size

Support Program/Read/Idle mode

RK2206 Datasheet Rev 1.1

1.2.6 External Storage Device Interface

SD/MMC Interface

Compatible with SD3.0, MMC ver4.51

Data bus width is 1bit

1.2.7 System Component

CRU (clock & reset unit)

One oscillator with 40MHz clock input

One 32.768KHz low power RC oscillator clock with trim function

Support 2 PLLs to generate all clocks

Support clock gating control for individual components

Support global soft-reset control for whole chip, also individual soft-reset for each component

PMU(power management unit)

3 separate power domains, which can be power up/down by software based on different application scenes

Multiple configurable work modes to save power by different frequency or automatic clock gating control or power domain on/off control

Support WLAN power save mode

Timer

Total Seven 64bits timers with interrupt-based operation

Support two operation modes: free-running and user-defined count

Support timer work state checkable

Watchdog

32-bit watchdog counter

Counter counts down from a preset value to 0 to indicate the occurrence of a timeout

WDT can perform two types of operations when timeout occurs:

Generate a system reset

First generate an interrupt and if this is not cleared by the service routine by the time a second timeout occurs then generate a system reset

Programmable reset pulse length

Total 16 defined-ranges of main timeout period

Three WDTs for Cortex-M4F, Cortex-M0 and DSP separately

MailBox

Two MailBoxs in RK2206 to service muti-core communication

Support four mailbox elements per mailbox, each element includes one data word, one command word register and one flag bit that can represent one interrupt

Provide muti-lock registers for software to use to indicate whether mailbox is occupied

DMAC

Support for memory-to-memory, memory-to-peripheral and peripheral-to-memory DMA transfers

Up to 6 channels, programmable channel priority

16 hardware request from peripherals, programmable hardware request priority

Multi-block transfers achieved through

Linked Lists (block chaining)

Auto-reloading of channel registers

Contiguous address between blocks

Support Scatter/Gather

Crypto Engine

RK2206 Datasheet Rev 1.1

Support SHA-1, SHA-256/224, SHA-512/384, MD5 with hardware padding

Support HMAC of SHA-1, SHA-256, SHA-512, MD5 with hardware padding

Support AES-128, AES-192, AES-256 encrypt & decrypt cipher

Support DES & TDES cipher

Support AES ECB/CBC/OFB/CFB/CTR/CTS/XTS/CCM/GCM/CBC-MAC/CMAC mode

Support DES/TDES ECB/CBC/OFB/CFB mode

Support up to 4096 bits PKA mathematical operations for RSA/ECC

Support up to 256 bits TRNG output

Temperature Sensor(TSADC)

Support one temperature sensor

Up to 50KS/s sampling rate

-40~125℃ temperature range and 5℃ temperature resolution

1.2.8 WLAN Subsystem

WLAN

IEEE 802.11b/g/n Radio, Baseband, Full Medium Access Control(Full MAC)

One Transmit and one Receive path(1T1R)

2.4GHz band and 20MHz bandwidth

Integrated TR switch, BALUN, LNA, and Power Amplifier

Support STA, AP and P2P operation modes

Support concurrent STA and P2P operation

Integrated TCP/IP Stack

Security support WEP, WPA, WPA2

Frame aggregation for increased MAC efficiency(A-MSDU,A-MPDU) and Low latency immediate High-Throughput Block Acknowledgement

Intelligent power control, including 802.11 power save mode

Dynamic power management based on packet signal quality

DSSS with DBPSK and DQPSK,CCK modulation

OFDM with BPSK, QPSK, 16QAM and 64QAM modulation. Convolutional Coding Rate:1/2, 2/3, 3/4 and 5/6

Maximum data rate 11Mbps for 802.11b, 54Mbps for 802.11g and 65Mbps(72.2Mbps in SGI mode) for 802.11n

Fast receiver Automatic Gain Control(AGC)

Support 96KB data buffer

1.2.9 Video Input Processor(VICAP)

VICAP

Support BT601 YCbCr 422 8-bit input

Support BT656 YCbCr 422 8-bit input

Support UYVY/VYUY/YUYV/YVYU configurable

Support RAW 8-bit input

Support window cropping

Support virtual stride when write to internal memory

Support different stored address for Y and UV

1.2.10 Video Output Processor(VOP)

VOP

Support RGB565/YUV420 source data format

Support YUV2RGB

Support RGB565 display data format

Support i8080 MCU interface

Support max output resolution 480×320

1.2.11 Audio Interface

I2S0

Connects to Chip IO

RK2206 Datasheet Rev 1.1

Up to 4 channels TX and 2 channels RX path

Support master mode and slave mode

Support I2S normal, left and right justified mode serial audio data transfer

Support PCM early, late1, late2, late3 mode serial audio data transfer

Support resolution from 16bits to 32bits

Sample rate up to 192KHz

I2S1

Connects to Audio Codec Controller inside Chip

Up to 2 channels TX and 4 channels RX path

Support master mode and slave mode

Support I2S normal, left and right justified mode serial audio data transfer

Support PCM early, late1, late2, late3 mode serial audio data transfer

Support resolution from 16bits to 32bits

Sample rate up to 192KHz

PDM

Support PDM master receive mode

Support 2 wire PDM interface with one is clock and 1 data line

Support up to 2 mono microphones or 1 stereo microphones

Support 16~24 bit sample resolution

Support sample rate up to 192KHz

Support programmable data sampling sensibility, rising or falling edge

Audio PWM

Support 2 channels audio PWM

Audio data width from 16bits to 32bits

Support audio resolution 8/9/10/11bits

Support linear interpolation by 2/4/6/8/16 oversampling

Support sample rate up to 16KHz

Voice Activity Detection(VAD)

Support single Mic human voice detection

Support human voice frequency band filtering

Support human voice amplitude detection

Support Muti-Mic array data store before voice detection event or after voice detection event two modes, and also can support Muti-Mic array data is not stored in voice detection process

Support Mic data from I2S0, I2S1 and PDM

Store memory is shared with system internal memory

Audio Codec Controller

Co-work with RK812 ASIC to provide full Audio Codec solution

Support mono line out for 24bit DAC

Support 2 channel microphone input and 1 channel AEC from 24bit ADC

Support I2S digital interface connected with I2S1

Support both I2S master and slave mode

Support 16bits/24bits resolution

Support sample rate

Group1: 8khz,16khz,32kHz,64kHz,128khz

Group2: 11.025khz,22.05khz,44.1khz,88.2khz,176.4khz

Group3: 12khz,24khz,48khz,96khz,192khz

1.2.12 Connectivity

USB 2.0 OTG

Compatible with USB 2.0 specification

Supports high-speed(480Mbps), full-speed(12Mbps) and low-speed(1.5Mbps) mode

RK2206 Datasheet Rev 1.1

SPI interface

Support two SPI Controller(SPI0/SPI1)

Support one chip-select for each SPI Controller

Support serial-master and serial-slave mode, software-configurable

I2C interface

Support three I2C interface(I2C0/I2C1/I2C2)

Support 7bits and 10bits address mode

Software programmable clock frequency

Data on the I2C-bus can be transferred at rates of up to 100 kbit/s in the Standard-mode, up to 400 kbit/s in the Fast-mode or up to 1 Mbit/s in Fast-mode Plus

UART Controller

Support three UART interface(UART0/UART1/UART2)

Embedded two 64-byte FIFO for TX and RX operation respectively

Support 5bit,6bit,7bit,8bit serial data transmit or receive

Standard asynchronous communication bits such as start, stop and parity

Support different input clock for UART operation to get up to 4Mbps baud rate

Support auto flow control mode

SPI2APB interface

Support slave mode SPI protocol

Support serial-slave mode only

Embedded a APB master interface

PWM

Three on-chip 4-channels PWM controllers with interrupt-based operation

Programmable pre-scaled operation to bus clock and then further scaled

Embedded 32-bit timer/counter facility

Support capture mode

Provides reference mode and output various duty-cycle waveform

Support continuous mode or one-shot mode

Optimized for IR application for last channel of each PWM controller

Touch Key Controller

Support muti-channel CapSense monitor

Support trigger interrupt waterline configurable

Support LPF and DC elimination

Multiple group of GPIO

All of GPIOs can be used to generate interrupt

Support level trigger and edge trigger interrupt

Support configurable polarity of level trigger interrupt

Support configurable rising edge, falling edge and both edge trigger interrupt

Support configurable pull direction(pull-up or pull-down)

Successive Approximation ADC (SARADC)

10-bit resolution

Up to 1MS/s sampling rate

8 single-ended input channels

RK2206 Datasheet Rev 1.1