瑞芯微RK3328芯片是一款专门面向中端影音市场的通用型SoC,支持主流格式的4K视频解码与输出,是三大开源平台之一,支持运行安卓系统、Linux系统和Linux发行版系统(Ubuntu、Debian等),非常适合定制项目。

1.1 Overview

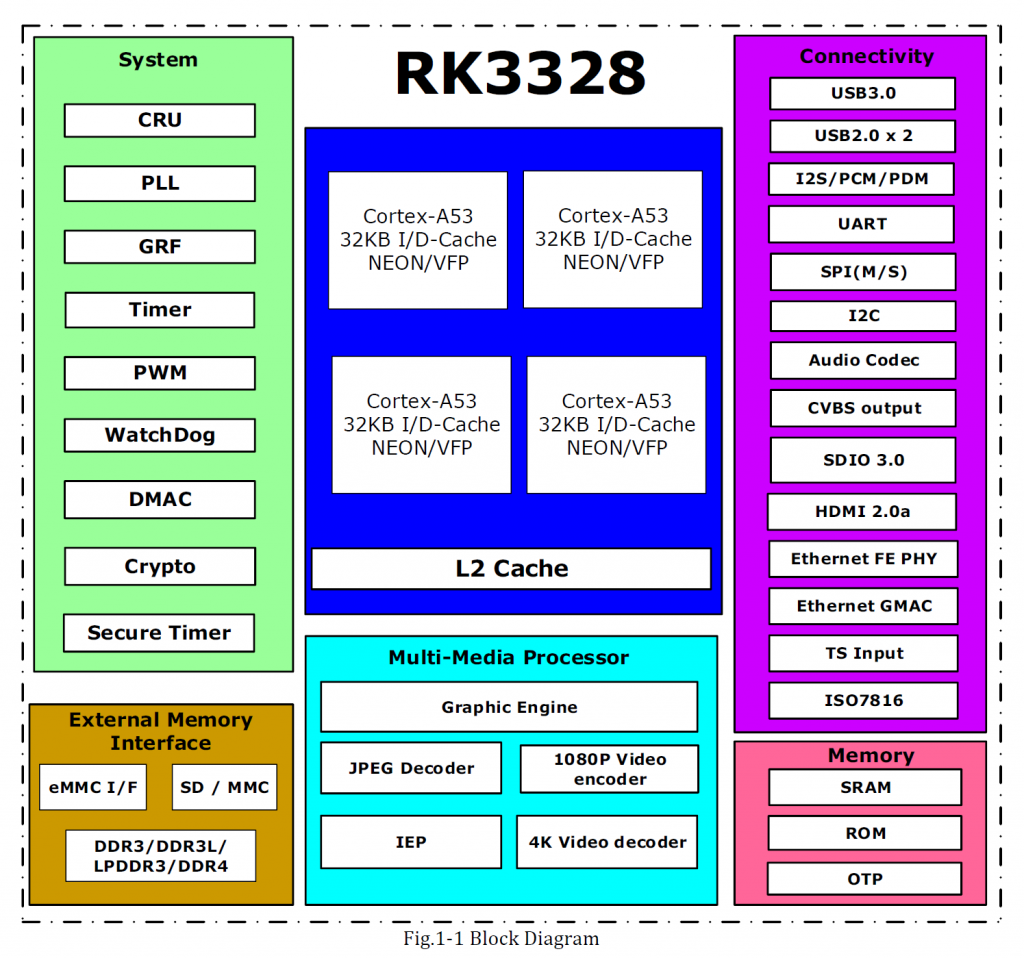

RK3328 is a high-performance Quad-core application processor designed for Smart STB (Set Top Box) including OTT/IPTV/DVB. It is a high-integration and cost efficient SOC for 4K HDR STB.

Quad-core Cortex-A53 is integrated with separate Neon and FPU coprocessor, also with shared L2 Cache. The Quad-core GPU supports high-resolution display and game.

Lots of high-performance interface to get very flexible solution, such as multi-channel display including HDMI2.0a and TV Encoder (CVBS). TrustZone and crypto hardware are integrated for security. 32bits DDR3/DDR3L/DDR4/LPDDR3 provides high memory bandwidth.

1.2 Features

The features listed below which may or may not be present in actual product, may be subject to the third-party licensing requirements. Please contact Rockchip for actual product feature configurations and licensing requirements.

- Microprocessor

- Quad-core ARM Cortex-A53 CPU

- Full implementation of the ARM architecture v8-A instruction set

- ARM Neon Advanced SIMD (single instruction, multiple data) support for accelerated media and signal processing computation

- ARMv8 Cryptography Extensions

- In-order pipeline with symmetric dual-issue of most instructions

- Unified system L2 cache

- Include VFP v3 hardware to support single and double-precision operations

- Integrated 32KB L1 instruction cache, 32KB L1 data cache with 4-way set associative

- TrustZone technology support

- Full CoreSight debug solution

- One separate power domains for CPU core system to support internal power switch and externally turn on/off based on different application scenario

- PD_A53: Cortex-A53 + Neon + FPU + L1 I/D Cache of core 2/3

- One isolated voltage domain to support DVFS

- Memory Organization

- Internal on-chip memory

- BootROM

- Internal SRAM

- External off-chip memory①

- DDR3/DDR3L/LPDDR3/DDR4

- SPI Flash

- eMMC

- SD

1.2.3 Internal Memory

- Internal BootRom

- Support system boot from the following device:

- SPI Flash interface

- eMMC interface

- SDMMC interface (SDMMC0 only)

- Support system boot from the following device:

- Support system code download by the following interface:

- USB OTG interface (Device mode)

- Internal SRAM

- Size: 36KB

1.2.4 External Memory or Storage device

- Dynamic Memory Interface (DDR3/DDR3L/LPDDR3/DDR4)

- Compatible with JEDEC standards

- Compatible with DDR3-1866 / DDR3L-1866 / LPDDR3 / DDR4

- Support 32-bit data width, 2 ranks (chip selects), max 4GB addressing space per rank; total addressing space is 4GB(max) also

- Programmable timing parameters to support SDRAM from various vendors

- Low power modes, such as power-down and self-refresh for SDRAM

- Compensation for board delays and variable latencies through programmable pipelines

- Programmable output and ODT impedance with dynamic PVT compensation

- eMMC Interface

- Compatible with standard iNAND interface

- Compatible with eMMC specification 4.41, 4.51, 5.0 and 1

- Support block size from 1 to 65535Bytes

- Support three data bus width: 1-bit, 4-bit or 8-bit

- Support up to HS200; but not support CMD Queue and HS400

- SD/MMC Interface

- There are 2 SD/MMC interface

- Compatible with SD3.0, MMC 51

- Support block size from 1 to 65535Bytes

- Data bus width is 4bits

1.2.5 System Component

- CRU (clock & reset unit)

- Support clock gating control for individual components

- One oscillator with 24MHz clock input

- Support global soft-reset control for whole SoC, also individual soft-reset for each component

- Timer

- Six 64bits timers with interrupt-based operation for non-secure application

- Two 64bits timers with interrupt-based operation for secure application

- Support two operation modes: free-running and user-defined count

- Support timer work state checkable

- PWM

- Four on-chip PWMs with interrupt-based operation

- Programmable pre-scaled operation to bus clock and then further scaled

- Embedded 32-bit timer/counter facility

- Support capture mode

- Support continuous mode or one-shot mode

- Provides reference mode and output various duty-cycle waveform

- Watchdog

- 32-bit watchdog counter

- Counter counts down from a preset value to 0 to indicate the occurrence of a timeout

- WDT can perform two types of operations when timeout occurs:

- Generate a system reset

- First generate an interrupt and if this is not cleared by the service routine by the time a second timeout occurs then generate a system reset

- Programmable reset pulse length

- Totally 16 defined-ranges of main timeout period

- Interrupt Controller

- Support 3 PPI interrupt source and 128 SPI interrupt sources input from different components

- Support 16 software-triggered interrupts

- Two interrupt outputs (nFIQ and nIRQ) separately for each Cortex-A53, both are low-level sensitive

- Support different interrupt priority for each interrupt source, and they are always software-programmable

- Trust Execution Environment system

- Support TrustZone technology for the following components

- Cortex-A53, support security and non-security mode, switch by software

- BUS_DMAC, support some dedicated channels work only in security mode

- Secure OTP, only can be accessed by Cortex-A53 in secure mode

- Internal memory, part of space is addressed only in security mode, detailed size is software-programmable together with TZMA (TrustZone memory adapter)

- Cipher engine

- Support TrustZone technology for the following components

u Support AES 128/192/256

- Supports the DES (ECB and CBC modes) and TDES (EDE and DED) algorithms

- Supports MD5, SHA-1 and SHA-256 HASH algorithms

- Support PKA(RSA) 512/1024/2048 bit Exp Modulator

- Support 160-bit Pseudo Random Number Generator (PRNG)

- Support 256-bit True Random Number Generator (TRNG)

- Support secure OTP

- Support secure boot

- Support secure debug

- Support secure OS

1.2.6 Video CODEC

- Video Decoder

- MMU embedded

- Real-time decoding of MPEG-1/2/4, H.264, H.265/HEVC, VC-1, AVS, AVS+

- 264/AVC Base/Main/High/High10 profile @ level 5.1; up to 4Kx2K @ 60fps

- 265/HEVC Main/Main10 profile @ level 5.1 High-tier; up to 4Kx2K @ 60fps

- VP9, up to 4Kx2K @ 60fps

- VP8, up to 1080P @ 60fps

n MPEG-1, ISO/IEC 11172-2, up to 1080P @ 60fps

- MPEG-2, ISO/IEC 13818-2, SP@ML, MP@HL, up to 1080P @ 60fps

n MPEG-4, ISO/IEC 14496-2, SP@L0-3, ASP@L0-5, up to 1080P @ 60fps

- VC-1, SP@ML, MP@HL, AP@L0-3, up to 1080P @ 60fps

- MVC is supported based on H.264 or H.265, up to 1080P @ 60fps

- 264 Video Encoder

- Support video encoder for H.264 at BP/MP/HP @ 2

- Resolution and frame rate are up to 1920×1080 @ 30FPS②

- 1x1080p @ 30fps or 2x720p @ 30fps encoding

- Only support I and P slices, not B slices

- 265 Video Encoder

- Capable of encoding HEVC Main Profile @ L5.0 High-tier

- Resolution and frame rate are up to 1920×1080 @ 30FPS②

- 1x1080p @ 30fps or 2x720p @ 30fps encoding

- Only support I and P slices, not B slices

- In-loop deblocking filtering

- Loop filtering across slice

- Noise reduction

- Rate Control: VBR, CBR and ABR; ROI support

1.2.7 Audio CODEC

- MP3, AAC, WMA, FLAC, OGG,

1.2.8 JPEG CODEC

- JPEG decoder

- Decoder size is from 48×48 to 8176×8176(66.8Mpixels)

- Support JPEG ROI (region of image) decode

- Embedded memory management unit(MMU)

1.2.9 Image Enhancement Processor (IEP)

- Data format support

- BT601_l/BT601_f/BT709_l/BT709_f color space conversion

- YUV up/down sampling

- De-interlace

- Max resolution is up to 1920×1080

- Configurable high frequency de-interlace

- I4O2 (Input 4 field, output 2 frame) /I4O1B/I4O1T/I2O1B/I2O1T mode

1.2.10 Graphics Engine

- 3D Graphics Engine:

- OpenGL ES 1.1 and 2.0, OpenVG1.1

- 2D Graphics Engine:

- Support Pixel Format conversion between 601 and BT.709

- Max resolution is 3840×2160

- BitBLT, operation with two data source

- Color fill with gradient fill, and pattern fill

- High-performance scaling and rotation concurrently

- Monochrome expansion for text rendering

- New comprehensive per-pixel alpha (color/alpha channel separately)

- Alpha blending modes including Java 2 Porter-Duff compositing blending rules, chroma key, pattern mask, fading

- Dither operation

- 0, 90, 180 and 270-degree rotation

- x-mirror and y-mirror rotation operation

1.2.11 Video input interface

- TS interface

- Support one TS input channel (serial mode or parallel mode)

- Support 4 TS input mode: sync/valid mode in the case of serial TS input, nosync/valid mode, sync/valid, sync/burst mode in the case of parallel TS input

- Supports 2 TS sources: demodulators and local memory

- Supports one PTI (Programmable Transport Interface):

- 64 PID filters

- TS descrambling with 16 sets of Control Word under CSA v2.0 standard

- 16 PES/ES filters with PTS/DTS extraction and ES start code detection

- 4/8 PCR extraction channels

- 64 Section filters with CRC check, and three interrupt mode: stop per unit, full- stop, recycle mode with version number check

- PID done and error interrupts for each channel

- PCR/DTS/PTS extraction interrupt for each channel

- Supports 1 PVR (Personal Video Recording) output channel

- 1 built-in multi-channel DMA Controller

- Independent MMU for this module

- Camera Interface

- Support up to 5M pixels

- 8bits BT656(PAL/NTSC) interface

- YUV422 data input format with adjustable YUV sequence

- YUV422, YUV420 output format with separately Y and UV space

- Support static histogram statistics and white balance statistics

- Support image crop with arbitrary windows

- Support scale up/down from 1/8 to 8 with arbitrary non-integer ratio

1.2.12 Display interface

- Display interface

- Support HDMI 2.0a output up to 4K@60Hz

- TV interface: TV encoder and DAC for CVBS

- HDMI

- Compliant with HDMI 0a

- Support up to 4k x 2k @ 60Hz

- Support 3D video formats

- Support 4K P60 YCbCr444, YCbCr422, YCbCr420 in 10-bit and 12-bit display

- Support HDCP 1.4 and 2

- TV out interface

- 10-bit resolution DAC

- Composite (CVBS) output

- 480i/576i standard definition output

1.2.13 Video Output Processor

- There is one VOP (Video Output Processor)

n 24-bit (RGB888 YCbCr444), 30-bit (RGB101010, YCbCr 420, YCbCr 444)

- Max output resolution 4K for HDMI, 480i/576i for CVBS

- 4 display layers:

- Display layers: Win0, Win1, HWC and background

- One background layer with programmable 24bits color

- There are two OSD/video layers (win0/win1)

- RGB888, ARGB888, RGB565, YCbCr422, YCbCr420, YCbCr444,YCbCr 420 10bit,YCbCr 422 10bit,YCbCr 444 10bit

- maximum resolution is 4096×2304, support virtual display

- 1/8 to 8 scaling up/down engine with arbitrary non-integer ratio

- 256 level alpha blending (pre-multiplied alpha support)

- Support transparency color key

- Support BG, RG, RB swap, x/y mirror

- Support TV Encoder for PAL and NTSC

- YCbCr2RGB(rec601-mpeg/rec601-jpeg/rec709)

- YCbCr2RGB(BT2020)

- RGB2YCbCr(BT601/BT709)

- RGB2YCbCr(BT2020)

- Conversion between BT2020 and BT709/601

- Win0 and Win1 layer overlay exchangeable

- Support replication (16bits to 24bits) and dithering (24bits to 16bits/ 18bits) operation

- Blank and blank display

- HDR is supported with HDR10 and HLG modes

- Support tone mapping between HDR and SDR, including HDR2SDR and SDR2HDR

1.2.14 Audio Interface

- I2S0/I2S1 with 8ch

- I2S0/I2S1 supports up to 8 channels (8xTX or 8xRX)

- I2S0 is connected to HDMI internally, while I2S1 is for external device

- Audio resolution from 16bits to 32bits

- Sample rate up to 192KHz

- Provides master and slave work mode, software configurable

- Support 3 I2S formats (normal, left-justified, right-justified)

- Support 4 PCM formats (early, late1, late2, late3)

- I2S and PCM mode cannot be used at the same time

- I2S2/PCM with 2ch

- Up to 2 channels (2xTX and 2xRX)

- Audio resolution from 16bits to 32bits

- Sample rate up to 192KHz

- Provides master and slave work mode, software configurable

- Support 3 I2S formats (normal, left-justified, right-justified)

- Support 4 PCM formats (early, late1, late2, late3)

- I2S and PCM cannot be used at the same time

- PDM

- Up to 8 channels

- SPDIF

- Support two 16-bit audio data store together in one 32-bit wide location

- Support bi-phase format stereo audio data output

- Support 16 to 31-bit audio data left or right justified in 32-bit wide sample data buffer

- Support 16, 20 and 24-bit audio data transfer in linear PCM mode

- Support non-linear PCM transfer

- Audio codec

- 24bit DAC

- Support Line-out

- Support Mono, Stereo

- Integrated digital interpolation and decimation filter

- Sampling rate of 8kHz/12kHz/16kHz/24kHz/32kHz/44.1KHz/48KHz/96KHz

1.2.15 Connectivity

- SDIO interface

- Compatible with SDIO 3.0 protocol

- 4bits data bus widths

- Smart Card

- support card activation and deactivation

- support cold/warm reset

- support Answer to Reset(ATR) response reception

- support T0 for asynchronous half-duplex character transmission

- support T1 for asynchronous half-duplex block transmission

- support automatic operating voltage class selection

- support adjustable clock rate and bit (baud) rate

- support configurable automatic byte repetition

- GMAC 10/100/1000M Ethernet Controller

- Supports 10/100/1000-Mbps data transfer rates with the RGMII interfaces

- Supports 10/100-Mbps data transfer rates with the RMII interfaces

- There are 2 controllers, one is connected to internal FE PHY, the other is for external PHY device

- Supports both full-duplex and half-duplex operation

- Supports IEEE 802.1Q VLAN tag detection for reception frames

- Support detection of LAN wake-up frames and AMD Magic Packet frames

- Handles automatic retransmission of Collision frames for transmission

- Ethernet PHY

- Integrated IEEE 802.3/802.3u compliant 10/100Mbps Ethernet PHY

- Supporting both full and half duplex for either 10 or 100 Mb/s data rate

- Auto MDIX capable

- Supports wake-on-LAN, EEE

- 100Base-FX support

- Supports auto-negotiation

- USB 0

- Built-in 2 USB 2.0 interfaces, one supports OTG

- Compatible with USB 2.0 specification

- Supports high-speed(480Mbps), full-speed(12Mbps) and low-speed(1.5Mbps) mode

- Provides 16 host mode channels

- Support periodic out channel in host mode

- USB 3.0 Host

- Support up to 64 devices

- Support 1 interrupter

- Support 1 USB2.0 port and 1 Super-Speed port

- Support standard or open-source xHCI and class driver

- Support xHCI Debug Capability

- SPI interface

- Support serial-master and serial-slave mode, software-configurable

- Support 1 chip-select output in serial-master mode

- I2C interface

- Support 7bits and 10bits address mode

- Software programmable clock frequency

- Data on the I2C-bus can be transferred at rates of up to 100 kbit/s in the Standard- mode, up to 400 kbit/s in the Fast-mode or up to 1 Mbit/s in Fast-mode

- UART Controller

- Embedded two 64-byte FIFO for TX and RX operation respectively

- Support 5bit,6bit,7bit,8bit serial data transmit or receive

- Standard asynchronous communication bits such as start, stop and parity

- Support different input clock for UART operation to get up to 4Mbps or another special baud rate

- Support auto flow control mode

- One IR remote controller input channel

1.2.16 Others

- Multiple group of GPIO

- All of GPIOs can be used to generate interrupt to CPU

- Temperature Sensor(TS-ADC)

- The SAR ADC up to 50KS/s sampling rate

- -20~120℃ temperature range and 5℃ temperature resolution

- OTP

- Support standby mode

- Provide inactive mode, VP must be 0V or Floating in this

- Package Type

- TFBGA395L (body: 14mm x 14mm; ball size: 0.3mm; ball pitch: 65mm)

RK3328 Datasheet Rev 1.4

Notes:

① DDR3/LPDDR2/LPDDR3/DDR4 are not used simultaneously

② Actual maximum frame rate will depend on the clock frequency and system bus performance

③ Actual maximum data rate will depend on the clock frequency and JPEG compression rate