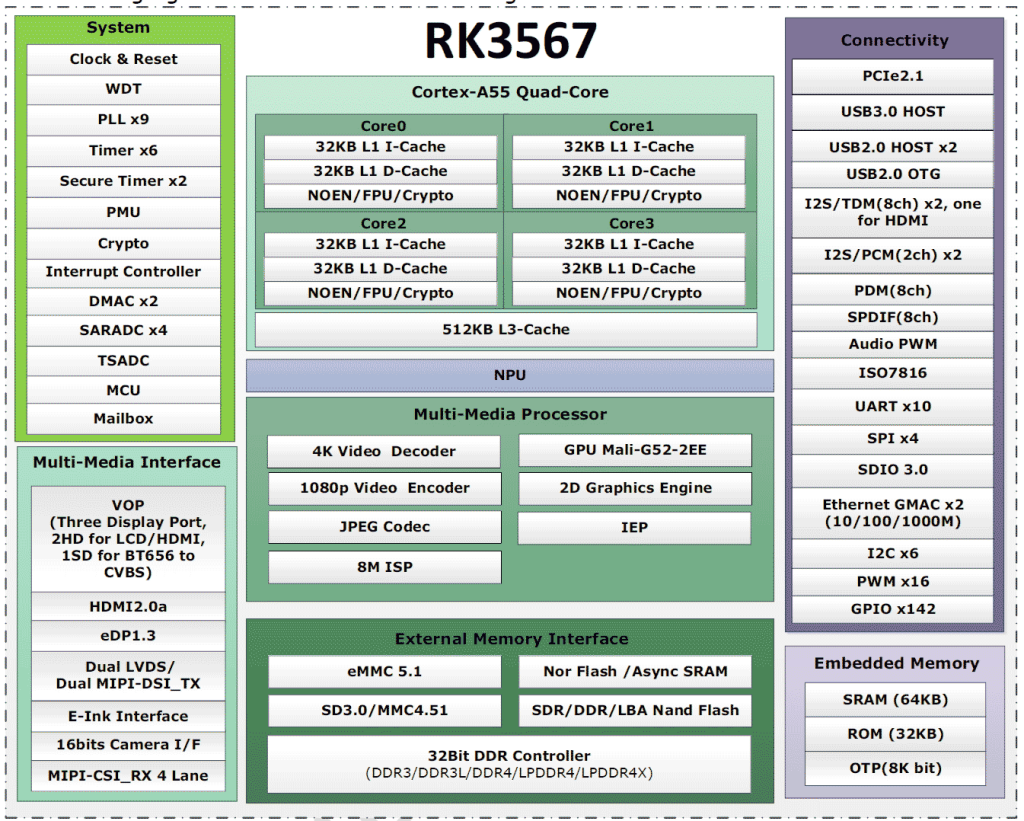

RK3567是瑞芯微旗下一款高性能、低功耗的四核应用处理器,专为个人移动互联网设备和AIoT设备设计。RK3567提供了许多嵌入式强大的硬件引擎,以优化高端应用程序的性能。RK3567产品定位接近RK3568,相比后者精简了一些接口,性价比更高,可以考虑迭代替换。下面是RK3567的datasheet,方便大家选型参考。

RK3567内置H.265解码器,支持4K@60fps解码,还支持H.264/H.265编码器1080p@60fps,高质量JPEG编码器/解码器。嵌入式3D GPU使RK3567与OpenGL ES 1.1/2.0/3.2、OpenCL 2.0和Vulkan 1.1完全兼容。特殊的2D硬件引擎将最大限度地提高显示性能,并提供非常平稳的操作。内置NPU支持INT8/INT16/FP16/BFP16 MAC混合操作。此外,由于其强大的兼容性,基于TensorFlow/MXNetPyTorch/Caffe等一系列框架的网络模型可以轻松转换。

RK3567具有高性能外部存储器接口(DDR3/DDR3L/DDR4/LPDDR3/LPDDR4/LPDDR4X),能够维持苛刻的存储器带宽。

1.2.1 Microprocessor

Quad-core ARM Cortex-A55 CPU

ARM Neon Advanced SIMD (single instruction, multiple data) support for accelerated media and signal processing computation

Include VFP hardware to support single and double-precision operations

ARMv8 Cryptography Extensions

Integrated 32KB L1 instruction cache, 32KB L1 data cache

512KB unified system L3 cache

TrustZone technology support

Separate power domains for CPU core system to support internal power switch and externally turn on/off based on different application scenario

PD_A55_0: 1st Cortex-A55 + Neon + FPU + L1 I/D Cache

PD_A55_1: 2nd Cortex-A55 + Neon + FPU + L1 I/D Cache

PD_A55_2: 3rd Cortex-A55 + Neon + FPU + L1 I/D Cache

PD_A55_3: 4th Cortex-A55 + Neon + FPU + L1 I/D Cache

One isolated voltage domain

1.2.2 Neural Process Unit

Neural network acceleration engine with processing performance up to 1 TOPS

Support INT8/INT16/FP16/BFP16 MAC hybrid operation

Support deeplearning frameworks: TensorFlow, TF-lite, Pytorch, Caffe, ONNX, MXNet, Keras, Darknet

One isolated voltage domain

1.2.3 Memory Organization

Internal on-chip memory

BootROM

SYSTEM_SRAM in the voltage domain of VD_LOGIC

PMU_SRAM in the voltage domain of VD_PMU for low power application

External off-chip memory

DDR3/DDR3L/DDR4/LPDDR3/LPDDR4/LPDDR4X①

RK3567 Datasheet Rev 1.0 by scensmart

SPI Nor/Nand Flash

eMMC

SD_Card

8bits Async Nand Flash

8bits toggle Nand Flash

8bits ONFI Nand Flash

1.2.4 Internal Memory

Internal BootRom

Support system boot from the following device:

SPI Flash interface

Nand Flash

eMMC interface

SDMMC interface

Support system code download by the following interface:

USB OTG interface (Device mode)

SYSTEM_SRAM

Size: 64KB

PMU_SRAM

Size: 8KB

1.2.5 External Memory or Storage device

Dynamic Memory Interface

Compatible with JEDEC standards

Compatible with DDR3-2133/DDR3L-2133/LPDDR3-2133/DDR4-3200/LPDDR4-3200/LPDDR4X-3200

Support 32bits data width, 2 ranks (chip selects), total addressing space is 8GB(max) for DDR3/DDR3L/DDR4

Support 32bits data width, 4 ranks (chip selects), total addressing space is 8GB(max) for LPDDR3/LPDDR4/LPDDR4X

Low power modes, such as power-down and self-refresh for SDRAM

Compensation for board delays and variable latencies through programmable pipelines

Programmable output and ODT impedance with dynamic PVT compensation

eMMC Interface

Compatible with standard iNAND interface

Compatible with eMMC specification 4.41, 4.51, 5.0 and 5.1

Support three data bus width: 1bit, 4bits or 8bits

Support HS200

Support CMD Queue

SD/MMC Interface

Compatible with SD3.0, MMC ver4.51

Data bus width is 4bits

Nand Flash Interface

Support async nand flash, each channel 8bits, up to 4 banks

Support ONFI Synchronous Flash Interface, each channel 8bits, up to 4 banks

Support Toggle Flash Interface, each channel 8bits, up to 4 banks

Support sync DDR nand flash, each channel 8bits, up to 4 banks

Support LBA nand flash in async or sync mode

Support SLC,MLC,2D/3D TLC nand flash

Up to 70bits/1KB hardware ECC

For DDR nand flash, support DLL bypass and 1/4 or 1/8 clock adjust, maximum clock rate is 75MHz RK3567 Datasheet Rev 1.0 by scensmart

For async nand flash, support configurable interface timing, maximum data rate is 16bits/cycle

SPI Flash Interface

Support Serial NOR Flash, NAND Flash, pSRAM and SRAM

Support SDR mode

Support 1bit/2bit/4bit data width

1.2.6 System Component

CRU (clock & reset unit)

Support clock gating control for individual components

One oscillator with 24MHz clock input

Support global soft-reset control for whole chip, also individual soft-reset for each component

MCU

32bits microcontroller core

Harvard architecture separate Instruction and Data memories

Integrated Programmable Interrupt Controller (IPIC)

Integrated Debug Controller with JTAG interface

PMU(power management unit)

5 separate voltage domains(VD_CORE/VD_LOGIC/VD_NPU/VD_GPU/VD_PMU)

15 separate power domains, which can be power up/down by software based on different application scenes

Multiple configurable work modes to save power by different frequency or automatic clock gating control or power domain on/off control

Timer

Six 64bits timers with interrupt-based operation for non-secure application

Two 64bits timers with interrupt-based operation for secure application

Support two operation modes: free-running and user-defined count

Support timer work state checkable

Watchdog

32bits watchdog counter

Counter counts down from a preset value to 0 to indicate the occurrence of a timeout

WDT can perform two types of operations when timeout occurs:

Generate a system reset

First generate an interrupt and if this is not cleared by the service routine by the time a second timeout occurs then generate a system reset

Programmable reset pulse length

Totally 16 defined-ranges of main timeout period

One Watchdog for non-secure application

One Watchdog for secure application

Interrupt Controller

Support 3 PPI interrupt sources and 256 SPI interrupt sources input from different components

Support 16 software-triggered interrupts

Two interrupt outputs (nFIQ and nIRQ) separately for each Cortex-A55, both are low-level sensitive

Support different interrupt priority for each interrupt source, and they are always software-programmable

RK3567 Datasheet Rev 1.0 by scensmart

Mailbox

One Mailbox in SoC to service Cortex-A55 and MCU communication

Support four mailbox elements per mailbox, each element includes one data word, one command word register and one flag bit that can represent one interrupt

Provide 32 lock registers for software to use to indicate whether mailbox is occupied

DMAC

Two identical DMAC blocks supported(DMAC0/DMAC1)

Micro-code programming based DMA

The specific instruction set provides flexibility for programming DMA transfers

Linked list DMA function is supported to complete scatter-gather transfer

Support internal instruction cache

Embedded DMA manager thread

Support data transfer types with memory-to-memory, memory-to-peripheral, peripheral-to-memory

Signals the occurrence of various DMA events using the interrupt output signals

Mapping relationship between each channel and different interrupt outputs is software-programmable

One embedded DMA controller for system

DMAC features:

8 channels totally

23 hardware request from peripherals

2 interrupt outputs

Trust Execution Environment system

Support TrustZone technology for the following components

Cortex-A55, support security and non-security mode, switch by software

System general DMAC, support some dedicated channels work only in security mode

Secure OTP, only can be accessed by Cortex-A55 in secure mode and secure key reader block

SYSTEM_SRAM, part of space is addressed only in security mode, detailed size is software-programmable together with TZMA (TrustZone memory adapter)

Cipher engine

Support SHA-1, SHA-256/224, SHA-512/384, MD5 with hardware padding

Support HMAC of SHA-1, SHA-256, SHA-512, MD5 with hardware padding

Support AES-128, AES-192, AES-256 encrypt & decrypt cipher

Support DES & TDES cipher

Support AES ECB/CBC/OFB/CFB/CTR/CTS/XTS/CCM/GCM/CBC-MAC/CMAC mode

Support DES/TDES ECB/CBC/OFB/CFB mode

Support up to 4096 bits PKA mathematical operations for RSA/ECC

Support data scrambling for DDR SDRAM device

Support up to 256 bits TRNG Output

Support secure OTP

Support secure boot

Support secure debug

Support secure OS

1.2.7 Video CODEC

Video Decoder

H.265 HEVC/MVC Main10 Profile yuv420@L5.1 up to 4096×2304@60fps

H.264 AVC/MVC Main10 Profile yuv400/yuv420/yuv422/@L5.1 up to 4096×2304@60fps

VP9 Profile0/2 yuv420@L5.1 up to 4096×2304@60fps

VP8 verision2,up to 1920×1088@60fps

RK3567 Datasheet Rev 1.0 by scensmart

VC1 Simple Profile@low, medium, high levels, Main Profile@low, medium, high levels, Advanced Profile@level0~3,up to 1920×1088@60fps

MPEG-4 Simple Profile@L0~6,Advanced Simple Profile@L0~5,up to 1920×1088@60fps

MPEG-2 Main Profile, low, medium and high levels, up to 1920×1088@60fps

MPEG-1 Main Profile, low, medium and high levels, up to 1920×1088@60fps

H.263 Profile0,levels 10-70,up to 720×576@60fps

Video Encoder

H.264/AVC BP/MP/HP@level4.2,,up to 1920×1080@60fps

H.265/HEVC MP@level4.1, up to 1920×1080@100fps (4096×4096@10fps with TILE)

Support YUV/RGB video source with rotation and mirror

1.2.8 JPEG CODEC

JPEG decoder

Decoder size is from 48×48 to 8192×8192

Support YUV400/YUV411/YUV420/YUV422/YUV440/YUV444

Support 1920×1080@120fps

Support MJPEG

JPEG encoder

Baseline Non-progressive

up to 8192×8192

up to 90 million pixels per second

1.2.9 Image Enhancement (IEP module)

Image format support

Input data: YUV420/YUV422 ; semi-planar/planar; UV swap

Output data: YUV420/YUV422 ; semi-planar; UV swap; Tile mode

YUV down sampling conversion from 422 to 420

Max resolution for dynamic image up to 1920×1080

De-interlace

I5O2: Input 5 Fields Output 2 frames mode

I5O1T: Input 5 Fields Output 1 Top frame mode

I5O1B: Input 5 Fields Output 1 Bottom frame mode

I2O2: Input 2 Fields Output 2 frames mode

I1O1T: Input 1 Field Output 1 Top frame mode

I1O1B: Input 1 Field Output 1 Bottom frame mode

PULLDOWN_REC: Pull down Recovery mode

DETECT_ONLY: Detect Only mode

MVHIST: De-interlace MV Histogram

MD: Motion Detection

ME: Motion Estimate

MC: Motion Compensation

EEDI: Enhanced Edge based Interpolation

OSD DETECT: On-Screen Display Detection

FF DETECT: Frame Field Detection

FO DETECT: Field Order Detection

PD DETECT: Pull down Detection

CC: Combining Check

1.2.10 Graphics Engine

3D Graphics Engine:

Mali-G52 1-Core-2EE

Support OpenGL ES 1.1, 2.0, and 3.2

RK3567 Datasheet Rev 1.0 by scensmart

Support Vulkan 1.0 and 1.1

Support OpenCL 2.0 Full Profile

Support 1600Mpix/s fill rate when 800MHz clock frequency

Support 38.4GLOPs when 800MHz clock frequency

2D Graphics Engine:

Data format

Support input of ARGB/RGB888/RGB565/RGB4444/RGB5551/YUV420/YUV422/YUYV;;

Support input of YUV422SP10bit/YUV420SP10bit(YUV-8bits out)

Support output of ARGB/RGB888/RGB565/RGB4444/RGB5551/YUV420/YUV422/YUYV;;

Pixel Format conversion, BT.601/BT.709

Dither operation, Y dither update;

Max resolution: 8192×8192 source, 4096×4096 destination

Scaling

Down-scaling: Average filter

Up-scaling: Bi-cubic filter(source>2048 would use Bi-linear)

Arbitrary non-integer scaling ratio,,from 1/16 to 16

Rotation

0, 90, 180, 270 degree rotation

x-mirror, y-mirror& rotation operation

BitBLT

Block transfer

Color palette/Color fill, support with alpha

Transparency mode (color keying/stencil test, specified value/value range)

Two source BitBLT:

A+B=B only BitBLT, A support rotate&scale when B fixed

A+B=C second source (B) has same attribute with (C) plus rotation function

Alpha Blending

New comprehensive per-pixel alpha(color/alpha channel separately)

Fading

SRC1(R2Y)&&SRC0(YUV)——alpha->DST(YUV)

1.2.11 Video input interface

Interface and video input processor

Support up to 16bit DVP interface (digital parallel input)

Support MIPI CSI RX interface

Support VICAP block(Video Input Processor)

Support video data from DVP

Support video data from MIPI CSI

Support DVP and MIPI CSI simultaneously

Support ISP block(Image Signal Processor)

Support video data from DVP

Support video data from MIPI CSI

DVP Interface

Support 8bits/10bits/12bits/16bits input

Support up to 150MHz input data

MIPI CSI RX Interface

Compatible with the MIPI Alliance Interface specification v1.2

Up to 4 data lanes, 2.5Gbps maximum data rate per lane

Support MIPI-HS, MIPI-LP mode

Support two mode

One interface with 1 clock lane and 4 data lanes

Two interface, each with 1 clock lane and 2 data lanes

RK3567 Datasheet Rev 1.0 by scensmart

VICAP

Support BT601 YCbCr 422 8bits input、、RAW 8/10/12bits input

Support BT656 YCbCr 422 8bits input

Support BT1120 YCbCr 422 8/10/12/16bits input, single/dual-edge sampling

Support 2/4 mixed BT656/BT1120 YCbCr 422 8bit input

Support YUYV sequence configurable

Support the polarity of pixel_clk, hsync and vsync configurable

Support receiving CSI2 protocol data(up to four IDs)

Support receiving DSI protocol data(Video mode/Command mode)

Support window cropping

Support virtual stride when write to DDR

Support NV16/NV12 output for YUV data

Support compact/ non-compact output for RAW data

ISP

DVP input: ITU-R BT601/656/1120 with raw8/raw10/raw12/raw16, YUV422

MIPI input: RX data lane x1/x2/x4, raw8/raw10/raw12, YUV422

3A: include AE/Histogram, AF, AWB statistics output

FPN: Fixed Pattern Noise removal

BLC: Black Level Correction

DPCC: Static/Dynamic defect pixel cluster correction

LSC: Lens shading correction

Bayer-2DNR: Bayer-raw De-noising, 2DNR Bayer-3DNR: Bayer-raw De-noising, 3DNR DRC: 2-Frame Merge Video Tone mapping

Debayer: Advanced Adaptive Demosaic with Chromatic Aberration Correction

CCM/CSM: Color correction matrix; RGB2YUV etc.

Gamma: Gamma out correction

Dehaze/Enhance: Automatic Dehaze and edge enhancement

3DLUT: 3D-Lut Color Palette for Customer

LDCH: Lens-distortion in the horizontal direction

2DNR: Advanced Spatial Noise reduce in YUV

Sharp: Picture Sharpening & Edge Enhance in YUV

CGC: Color Gamut Compression, YUV full range/limit range convert

Output Scale*2

Maximum resolution is 4096×2304

1.2.12 Display interface

Display interface

Support BT656/BT1120 interface

Support MIPI_DSI interface

Support LVDS interface(Combo with MIPI_DSI)

Support HDMI interface

Support eDP interface

Support EBC inteface

Support three simultaneous displays in the following interfaces

BT1120/BT656

MIPI_DSI_TX

LVDS

HDMI

eDP

MIPI DSI TX interface

Compatible with MIPI Alliance Interface specification v1.2

Support 2 channel DSI

Support 4 data lanes per channel

Support 2.5Gbps maximum data rate per lane

RK3567 Datasheet Rev 1.0 by scensmart

Up to 1920×1080@60Hz display output for single MIPI mode and 2560*1440@60Hz for dual-MIPI mode

Support RGB(up to 8bit) format

LVDS interface

Compliant with the TIA/EIA-644-A LVDS specification

Support dual LVDS interfaces

Support RGB888 and RGB666 input for LVDS interface

Support VESA/JEIDA LVDS data format transfer

HDMI TX interface

Single Physical Layer PHY with support for HDMI1.4 and HDMI2.0 operation

For HDMI operation, support for the following:

HPD input analog comparator

13.5–600MHz input reference clock

Up to 10 bits Deep Color modes

Up to 18Gbps aggregate bandwidth

Up to 1080p@120Hz and 4096×2304@60Hz

3-D video formats

Support RGB/YUV(up to 10bit) format

Support HDCP1.4/2.2

eDP interface

Support 1 eDP 1.3 interface

Up to 4 physical lanes of 2.7Gbps

Supports Panel Self Refresh(PSR)

Support up to 2560×1600@60Hz

Support RGB(up to 10bit) format

1.2.13 Video Output Processor

Video inputs

Support 2 cluster layer

Support up to 4096×2160 input resolution

Support afbcd

Support RGB/YUV/YUYV format

Support scale up/down ratio 4~1/4

Support rotation

Support 2 esmart layer

Support up to 4096×2160 input resolution

Support RGB/YUV/YUYV format

Support scale up/down ratio 4~1/4

Support 4 regions

Support 2 smart layer

Support up to 4096×2160 input resolution

Support RGB format

Support 4 regions

Overlay

Support MAX 6 layers overlay: 2 Cluster/2 ESMART/2 SMART

Support RGB/YUV domain overlay

Post process

HDR

HDR10/HDR HLG

HDR2SDR/SDR2HDR

3D-LUT/P2I/CSC/BCSH/DITHER/CABC/GAMMA/COLORBAR

Write back

Format: ARGB8888/RGB888/RGB565/YUV420

Max resolution: 1920×1080

Video outputs

Video output0, up to 4096×2304@60Hz resolution

Video output1, up to 2048×1536@60Hz resolution

RK3567 Datasheet Rev 1.0 by scensmart

Video output2, up to 1920×1080@60Hz resolution

Note: Three display monitors can be driven simultaneously, but the actual output performance is subject to the GPU capability and DDR bandwidth, which requires the comprehensive evalution of the UI resolution, frame rate and image layer quantity.

1.2.14 Audio Interface

I2S0 with 8 channel

Up to 8 channels TX and 8 channels RX path

Audio resolution from 16bits to 32bits

Sample rate up to 192KHz

Provides master and slave work mode, software configurable

Support 3 I2S formats (normal, left-justified, right-justified)

Only for HDMI inside

I2S1 with 8 channel

Up to 8 channels TX and 8 channels RX path

Audio resolution from 16bits to 32bits

Sample rate up to 192KHz

Provides master and slave work mode, software configurable

Support 3 I2S formats (normal, left-justified, right-justified)

Support 4 PCM formats (early, late1, late2, late3)

I2S and PCM mode cannot be used at the same time

I2S2/I2S3 with 2 channel

Up to 2 channels for TX and 2 channels RX path

Audio resolution from 16bits to 32bits

Sample rate up to 192KHz

Provides master and slave work mode, software configurable

Support 3 I2S formats (normal, left-justified, right-justified)

Support 4 PCM formats (early, late1, late2, late3)

I2S and PCM cannot be used at the same time

PDM

Up to 8 channels

Audio resolution from 16bits to 24bits

Sample rate up to 192KHz

Support PDM master receive mode

TDM

supports up to 8 channels for TX and 8 channels RX path

Audio resolution from 16bits to 32bits

Sample rate up to 192KHz

Provides master and slave work mode, software configurable

Support 3 I2S formats (normal, left-justified, right-justified)

Support 4 PCM formats (early, late1, late2, late3)

1.2.15 Connectivity

SDIO interface

Compatible with SDIO3.0 protocol

4bits data bus widths

MAC 10/100/1000 Ethernet Controller

Support two identical Ethernet controllers

Support 10/100/1000 Mbps data transfer rates with the RGMII interfaces

Support 10/100 Mbps data transfer rates with the RMII interfaces

Support both full-duplex and half-duplex operation

Supports IEEE 802.1Q VLAN tag detection for reception frames

RK3567 Datasheet Rev 1.0 by scensmart

Support detection of LAN wake-up frames and AMD Magic Packet frames

Support checking IPv4 header checksum and TCP, UDP, or ICMP checksum encapsulated in IPv4 or IPv6 datagram

Support for TCP Segmentation Offload (TSO) and UDP Fragmentation Offload (UFO)

USB 2.0 OTG

Compatible Specification

Universal Serial Bus Specification, Revision 2.0

Extensible Host Controller Interface for Universal Serial Bus (xHCI), Revision 1.1

Support Control/Bulk/Interrupt/Isochronous Transfer

USB 2.0 Host

Support two USB2.0 Host

Compatible with USB 2.0 specification

Supports high-speed(480Mbps), full-speed(12Mbps) and low-speed(1.5Mbps) mode

Support Enhanced Host Controller Interface Specification (EHCI), Revision 1.0

Support Open Host Controller Interface Specification (OHCI), Revision 1.0a

Multi-PHY Interface

Support two multi-PHYs with PCIe2.1/USB3.0

Up to one USB3 Host controller

Up to one PCIe2.1 controller

Multi-PHY1 support the following interfaces

USB3.0 Host

Multi-PHY2 support the following interfaces

PCIe2.1

USB 3.0 xHCI Host Controller

Support 1 USB2.0 port and 1 Super-Speed port

Concurrent USB3.0/USB2.0 traffic, up to 8.48Gbps bandwidth

Support standard or open-source xHCI and class driver

PCIe2.1 interface

Compatible with PCI Express Base Specification Revision 3.0

Support Root Complex(RC) mode

Support 2.5Gbps and 5.0Gbps serial data transmission rate per lane per direction

Support one lane

SPI interface

Support four SPI Controller

Support one chip-select output and the other support two chip-select output

Support serial-master and serial-slave mode, software-configurable

I2C interface

Support six I2C interface

Support 7bits and 10bits address mode

Software programmable clock frequency

Data on the I2C-bus can be transferred at rates of up to 100Kbit/s in the Standard-mode, up to 400Kbit/s in the Fast-mode or up to 1 Mbit/s in Fast-mode Plus.

UART Controller

Support ten UART interfaces

Embedded two 64-byte FIFO for TX and RX operation respectively

Support 5bits,6bits,7bits,8bits serial data transmit or receive

Standard asynchronous communication bits such as start, stop and parity

Support different input clock for UART operation to get up to 4Mbps baud rate

Support auto flow control mode for UART0/UART1/UART3/UART4/UART5

RK3567 Datasheet Rev 1.0 by scensmart

PWM

Sixteen on-chip PWMs(PWM0~PWM15) with interrupt-based operation

Programmable pre-scaled operation to bus clock and then further scaled

Embedded 32bits timer/counter facility

Support capture mode

Support continuous mode or one-shot mode

Provides reference mode and output various duty-cycle waveform

Optimized for IR application for PWM3,PWM7,PWM11 and PWM15

Smart Card

Support ISO-7816

support card activation and deactivation

support cold/warm reset

support Answer to Reset(ATR) response reception

support T0 for asynchronous half-duplex character transmission

support T1 for asynchronous half-duplex block transmission

support automatic operating voltage class selection

support adjustable clock rate and bit (baud) rate

support configurable automatic byte repetition

1.2.16 Others

Multiple group of GPIO

All of GPIOs can be used to generate interrupt to CPU

Support level trigger and edge trigger interrupt

Support configurable polarity of level trigger interrupt

Support configurable rising edge, falling edge and both edge trigger interrupt

Temperature Sensor(TSADC)

Up to 50KS/s sampling rate

Support two temperature sensor

-20~120℃℃ temperature range and 5℃℃ temperature resolution

Support two channels

Successive Approximation ADC (SARADC)

10bits resolution

Up to 1MS/s sampling rate

4 single-ended input channels

OTP

Support 8K bits Size, 7K bits for secure application

Support Program/Read/Idle mode

Package Type

FCCSP565L (body: 15.5mm x 14.4mm; ball size: 0.25mm; ball pitch: 0.65&0.4mm)