日前,JEDEC固态技术协会发布了下一代主流存储器标准DDR5 SDRAM的最终规范,这将标志着计算机存储器开发的一个重要里程碑。自90年代末以来,DDR的最新版本一直在驱动PC,服务器以及所有产品之间的发展,DDR5再次扩展了DDR内存的功能,使峰值内存速度提高了一倍,同时也大大增加了内存大小。随着DDR5 SDRAM最终规范的发布,各种硬件必将迎来新一轮升级,获取更强大的性能。预计到2021年,基于新标准的硬件将在服务器级别开始采用,然后再推广到客户端PC和其他设备。

各代DDR的主要规格对比:

| JEDEC DDR Generations | ||||

| DDR5 | DDR4 | DDR3 | LPDDR5 | |

| Max Die Density | 64 Gbit | 16 Gbit | 4 Gbit | 32 Gbit |

| Max UDIMM Size | 128 GB | 32 GB | 8 GB | N/A |

| Max Data Rate | 6.4 Gbps | 3.2 Gbps | 1.6 Gbps | 6.4Gbps |

| Channels | 2 | 1 | 1 | 1 |

| Width (Non-ECC) | 64-bits (2×32) | 64-bits | 64-bits | 16-bits |

| Banks (Per Group) | 4 | 4 | 8 | 16 |

| Bank Groups | 8/4 | 4/2 | 1 | 4 |

| Burst Length | BL16 | BL8 | BL8 | BL16 |

| Voltage (Vdd) | 1.1V | 1.2V | 1.5V | 1.05V |

| Vddq | l.lV | 1.2V | 1.5V | 0.5V |

DDR5规范最初计划于2018年发布,虽然最终版本的发布日期相对于JEDEC的原定计划有些落后,但并没有降低新存储器规范的重要性。像之前的DDR每次迭代一样,DDR5的主要重点再次是提高内存密度和速度。JEDEC希望将两者都提高一倍,最大内存速度设置为至少6.4Gbps,而单个封装的LRDIMM的容量最终将达到2TB。

封装变得更大:更密的内存和芯片堆叠

DDR5将允许单个存储芯片达到64Gbit的密度,这比DDR4的最大16Gbit密度高出4倍。结合die堆叠,可以将多达8个管芯die为一个芯片,那么40个单元的LRDIMM可以达到2TB的有效存储容量。或者对于更不起眼的无缓冲DIMM,这意味着我们最终将看到典型双列配置的DIMM容量达到128GB。

当然,当芯片制造赶上规范允许的范围时,DDR5规范的峰值容量将用于该标准生命周期的后期。首先,内存制造商将使用当今可达到的密度8Gbit和16Gbit芯片来构建其DIMM。因此,虽然DDR5的速度提升将是相当立即的,但是随着制造密度的提高,容量的提升将更加缓慢。

更快:一个DIMM,两个通道

DDR5的另一部分是关于再次增加内存带宽。JEDEC预计DDR5将以4.8Gbps的速度推出,比DDR4的官方3.2Gbps最大速度快约50%。在随后的几年中,该规范的当前版本允许的数据速率高达6.4Gbps,是DDR4官方峰值的两倍。这些速度目标的基础是DIMM和内存总线上的更改,以便每个时钟周期馈送和传输大量数据。与DRAM速度一样,最大的挑战来自DRAM核心时钟速率缺乏进展。专用逻辑仍在变得越来越快,存储器总线也在变得越来越快,但是支撑现代存储器的基于电容器和晶体管的DRAM的时钟频率仍然不能超过几百兆赫兹。

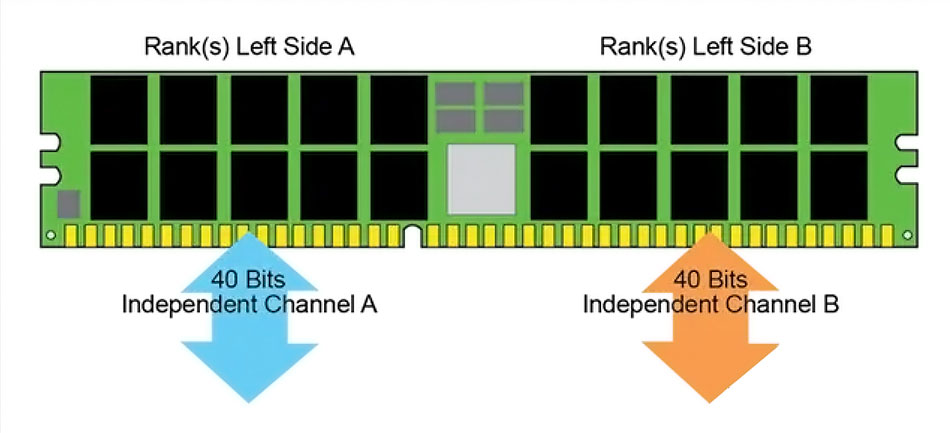

为了从DRAM裸片中获得更多收益,需要越来越多的并行性。DDR5在LPDDR4和GDDR6等其他标准中看到的情况类似,单个DIMM被分解为2个通道。DDR5不会为每个DIMM提供一个64位数据通道,而是为每个DIMM提供两个独立的32位数据通道(考虑ECC时为40位)。同时,每个通道的burst length从8字节(BL8)翻倍到16字节(BL16),这意味着每个通道每次操作将交付64字节。与DDR4 DIMM相比,以两倍于额定内存速度(相同核心速度)运行的DDR5 DIMM将在DDR4 DIMM传输一个DDR4 DIMM的时间内提供两个64字节操作,从而使有效带宽增加了一倍。

快速总线服务:决策反馈均衡

相比寻找增加DRAM DIMM并行化数量的方法,增加总线速度既简单又困难:这种想法在概念上很简单,在执行上也很困难。最终,要使DDR的内存速度提高一倍,DDR5的内存总线的运行速度必须是DDR4的两倍。DDR5进行了几处更改以实现这一目标,但是令人惊讶的是,存储总线没有任何大规模的根本更改,例如QDR或差分信令(differential signaling)。取而代之的是,JEDEC及其成员已经能够使用经过稍微修改的DDR4总线版本实现其目标,尽管这种总线必须在更严格的公差范围内运行。

这里的关键驱动因素是决策反馈均衡(Decision Feedback Equalization:DFE)的引入。在非常高的水平上,DFE是一种通过使用来自内存总线接收器的反馈来提供更好的均衡效果来减少 inter-symbol 干扰的方法。更好的均衡又可以使DDR5内存总线以更高的传输速率运行所需的更清晰的信号传输,而不会发生任何故障。同时,标准中的一些较小更改进一步帮助了这一点,例如添加了新的改进训练模式,以帮助DIMM和控制器补偿内存总线上的微小时序差异。

更简单的主板,更复杂的DIMM:DIMM上的电压调节

随着内核在密度和存储速度方面的变化,DDR5再次提高了DDR存储器的工作电压。根据规格,DDR5的Vdd为1.1v,低于DDR4的1.2v。像过去的更新一样,这将提高内存相对于DDR4的电源效率,尽管到目前为止,功耗提升的幅度不如DDR4和早期标准。JEDEC还在DDR5内存标准中引入来对DIMM的电压调节方式进行相当重要的更改。简而言之,电压调节正从主板移至各个DIMM,而DIMM则负责其自身的电压调节需求。这意味着DIMM现在将包括一个集成的稳压器,并且适用于从UDIMM到LRDIMM的所有内容。

DDR5 DIMM:仍为288针,但引脚排列已更改

最后,正如早期供应商原型中已经广泛证明的那样,DDR5将保持与DDR4相同的288针数。这反映了DDR2到DDR3的过渡,此处的引脚数在240个引脚处也保持相同。但是,不要期望在DDR4插槽中使用DDR5 DIMM。尽管引脚数没有改变,但引脚排列却是为了适应DDR5的新功能,尤其是其双通道设计。

现在开始送样,在接下来的12-18个月内开始采用

随着DDR5准备发布,可以期望主要的存储器制造商继续炫耀其原型和商用DIMM。随着2021年正式开始采用,似乎明年将为服务器市场以及最终的客户端台式机市场带来一些有趣的变化。