UCIe网站:https://www.uciexpress.org

UCIe网站:https://www.uciexpress.org

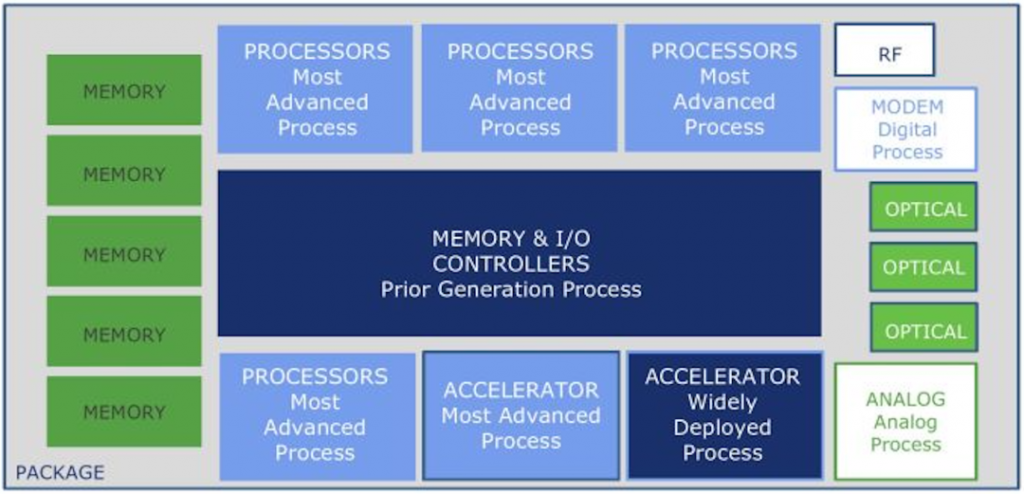

借助chiplet技术,一个大型芯片不需要全部使用昂贵的7nm、5nm等先进制程,而是可以根据自身需求,混合搭配由多个芯片制造商、多个制程节点制造的芯片模块,将它们封装在一起。这样既有助于提高效率,又减少了经济负担。对性能与效率的追求,也驱使人们对chiplet产生持续的兴趣。PCIe按照芯片标准来看偏慢,延迟较高,且数据传输能耗偏高,因此芯片制造商希望将更多功能集成到芯片中来降低延迟和功耗。如果用chiplet实现,这或许能将性能提高20倍以上,或者将功耗降为原来的1/20。

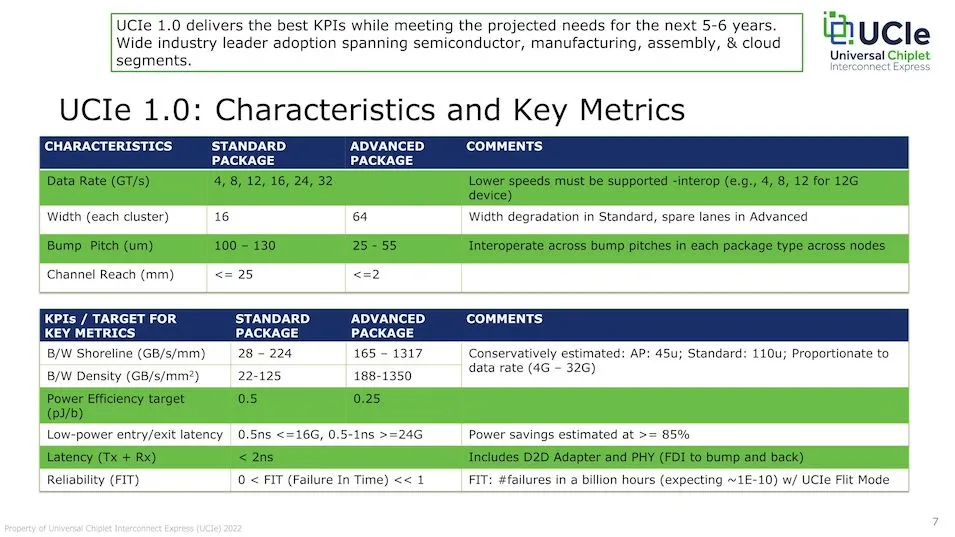

借助chiplet技术,一个大型芯片不需要全部使用昂贵的7nm、5nm等先进制程,而是可以根据自身需求,混合搭配由多个芯片制造商、多个制程节点制造的芯片模块,将它们封装在一起。这样既有助于提高效率,又减少了经济负担。对性能与效率的追求,也驱使人们对chiplet产生持续的兴趣。PCIe按照芯片标准来看偏慢,延迟较高,且数据传输能耗偏高,因此芯片制造商希望将更多功能集成到芯片中来降低延迟和功耗。如果用chiplet实现,这或许能将性能提高20倍以上,或者将功耗降为原来的1/20。 新UCIe互连的外观和操作类似于on-die连接,同时还支持与其他组件的off-die连接。这些设计甚至可以为机架规模的设计提供足够低的延迟和足够高的带宽。在协议层,芯片制造商有几种不同选择。UCIe的官方标准协议是成熟的PCIe和开放的CXL(Compute eXpress Link)。

新UCIe互连的外观和操作类似于on-die连接,同时还支持与其他组件的off-die连接。这些设计甚至可以为机架规模的设计提供足够低的延迟和足够高的带宽。在协议层,芯片制造商有几种不同选择。UCIe的官方标准协议是成熟的PCIe和开放的CXL(Compute eXpress Link)。